PCI-to-PCI Bridge Registers (D30:F0)

422 Datasheet

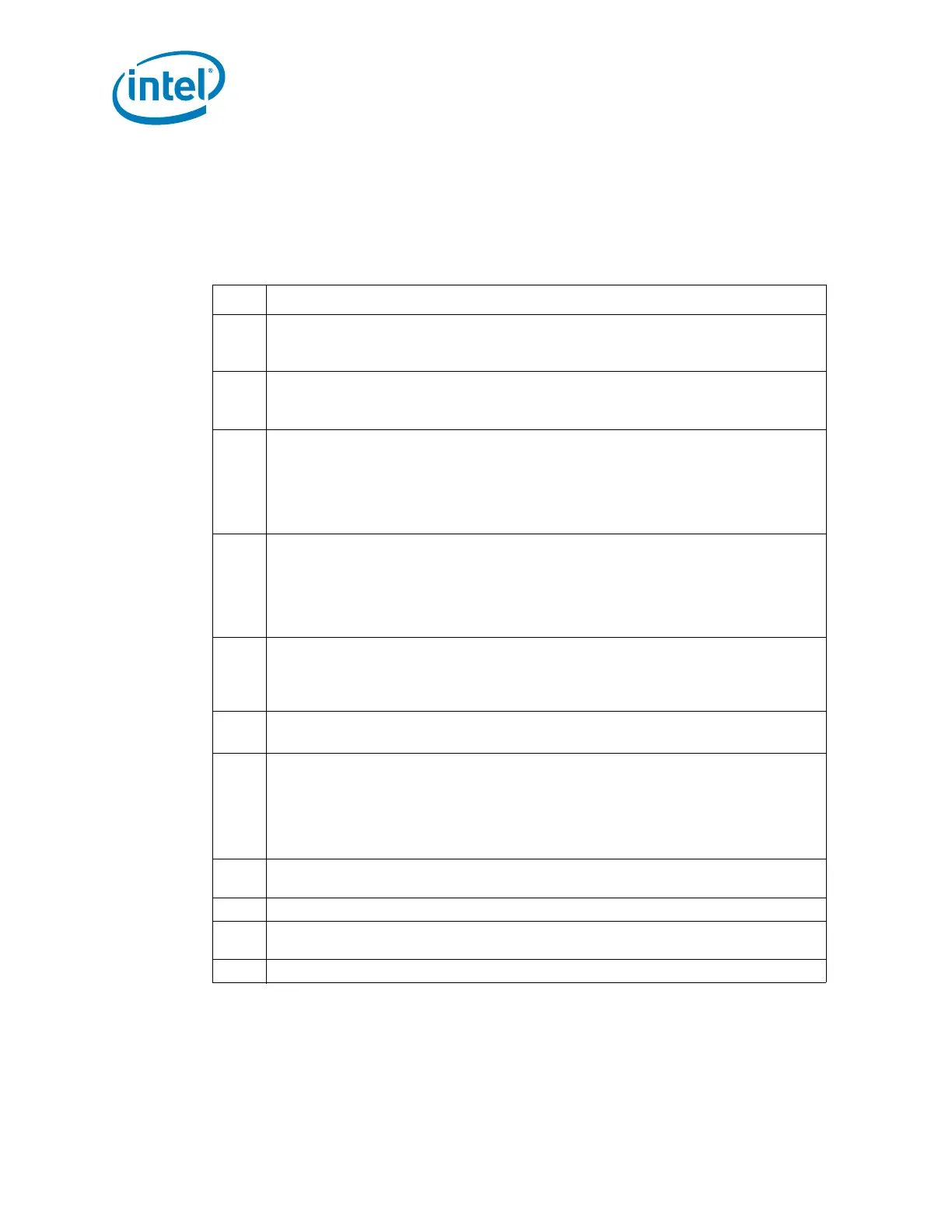

11.1.12 SECSTS—Secondary Status Register (PCI-PCI—D30:F0)

Offset Address: 1Eh–1Fh Attribute: R/WC, RO

Default Value: 0280h Size: 16 bits

Note: For the writable bits, software must write a 1 to clear bits that are set. Writing a 0 to

the bit has no effect.

Bit Description

15

Detected Parity Error (DPE) — R/WC.

0 = Parity error not detected.

1 = PCH PCI bridge detected an address or data parity error on the PCI bus

14

Received System Error (RSE) — R/WC.

0 = SERR# assertion not received

1 = SERR# assertion is received on PCI.

13

Received Master Abort (RMA) — R/WC.

0 = No master abort.

1 = This bit is set whenever the bridge is acting as an initiator on the PCI bus and the

cycle is master-aborted. For processor/PCH interface packets that have completion

required, this must also cause a target abort to be returned and sets PSTS.STA.

(D30:F0:06 bit 11)

12

Received Target Abort (RTA) — R/WC.

0 = No target abort.

1 = This bit is set whenever the bridge is acting as an initiator on PCI and a cycle is

target-aborted on PCI. For processor/PCH interface packets that have completion

required, this event must also cause a target abort to be returned, and sets

PSTS.STA. (D30:F0:06 bit 11).

11

Signaled Target Abort (STA) — R/WC.

0 = No target abort.

1 = This bit is set when the bridge is acting as a target on the PCI Bus and signals a

target abort.

10:9

DEVSEL# Timing (DEVT) — RO.

01h = Medium decode timing.

8

Data Parity Error Detected (DPD) — R/WC.

0 = Conditions described below not met.

1 = The PCH sets this bit when all of the following three conditions are met:

• The bridge is the initiator on PCI.

• PERR# is detected asserted or a parity error is detected internally

• BCTRL.PERE (D30:F0:3E bit 0) is set.

7

Fast Back to Back Capable (FBC) — RO. Hardwired to 1 to indicate that the PCI to PCI

target logic is capable of receiving fast back-to-back cycles.

6 Reserved

5

66 MHz Capable (66MHZ_CAP) — RO. Hardwired to 0. This bridge is 33 MHz capable

only.

4:0 Reserved

Loading...

Loading...