Datasheet 421

PCI-to-PCI Bridge Registers (D30:F0)

11.1.10 SMLT—Secondary Master Latency Timer Register

(PCI-PCI—D30:F0)

Offset Address: 1Bh Attribute: R/W

Default Value: 00h Size: 8 bits

This timer controls the amount of time the PCH PCI-to-PCI bridge will burst data on its

secondary interface. The counter starts counting down from the assertion of FRAME#.

If the grant is removed, then the expiration of this counter will result in the deassertion

of FRAME#. If the grant has not been removed, then the PCH PCI-to-PCI bridge may

continue ownership of the bus.

11.1.11 IOBASE_LIMIT—I/O Base and Limit Register

(PCI-PCI—D30:F0)

Offset Address: 1Ch–1Dh Attribute: R/W, RO

Default Value: 0000h Size: 16 bits

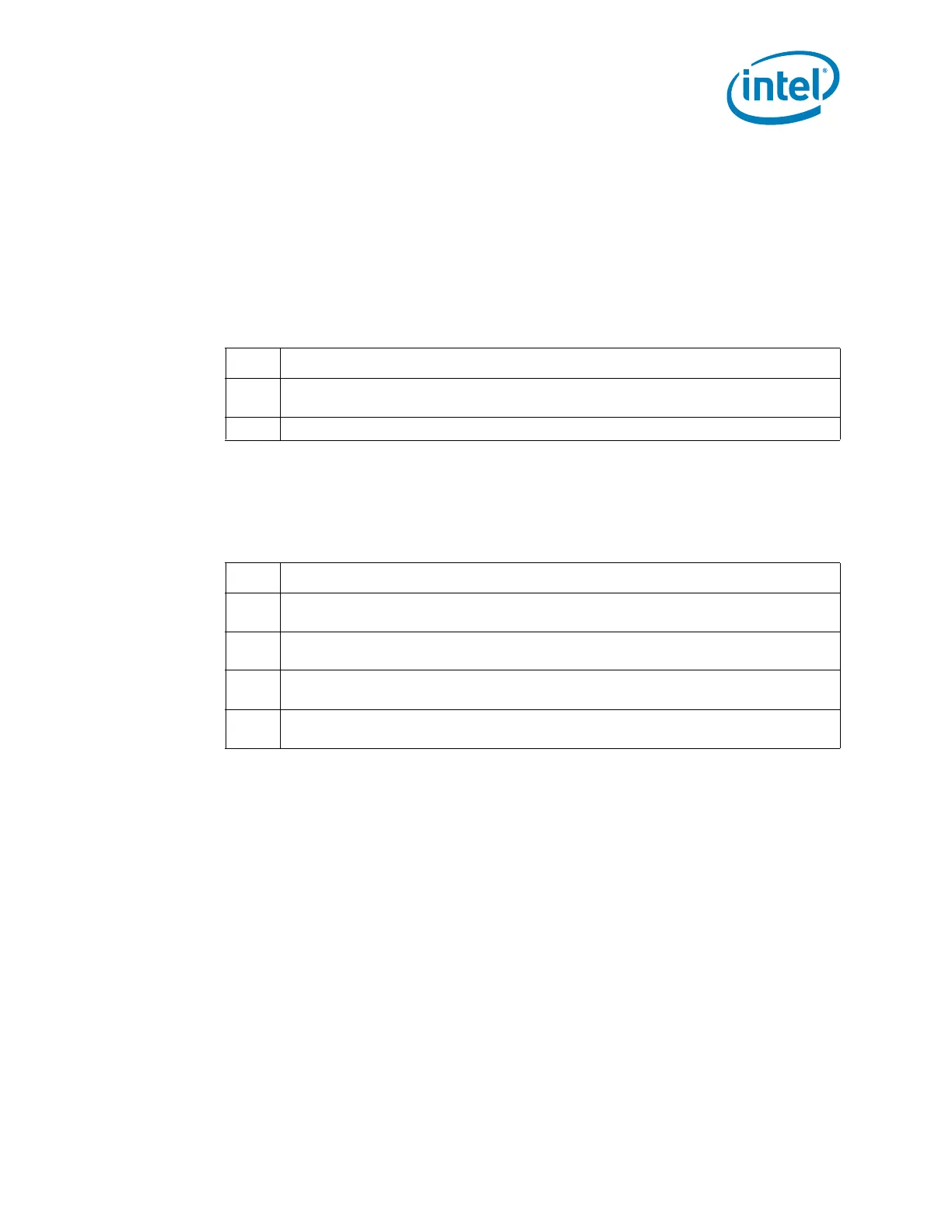

Bit Description

7:3

Master Latency Timer Count (MLTC) — R/W. This 5-bit field indicates the number of

PCI clocks, in 8-clock increments, that the PCH remains as master of the bus.

2:0 Reserved

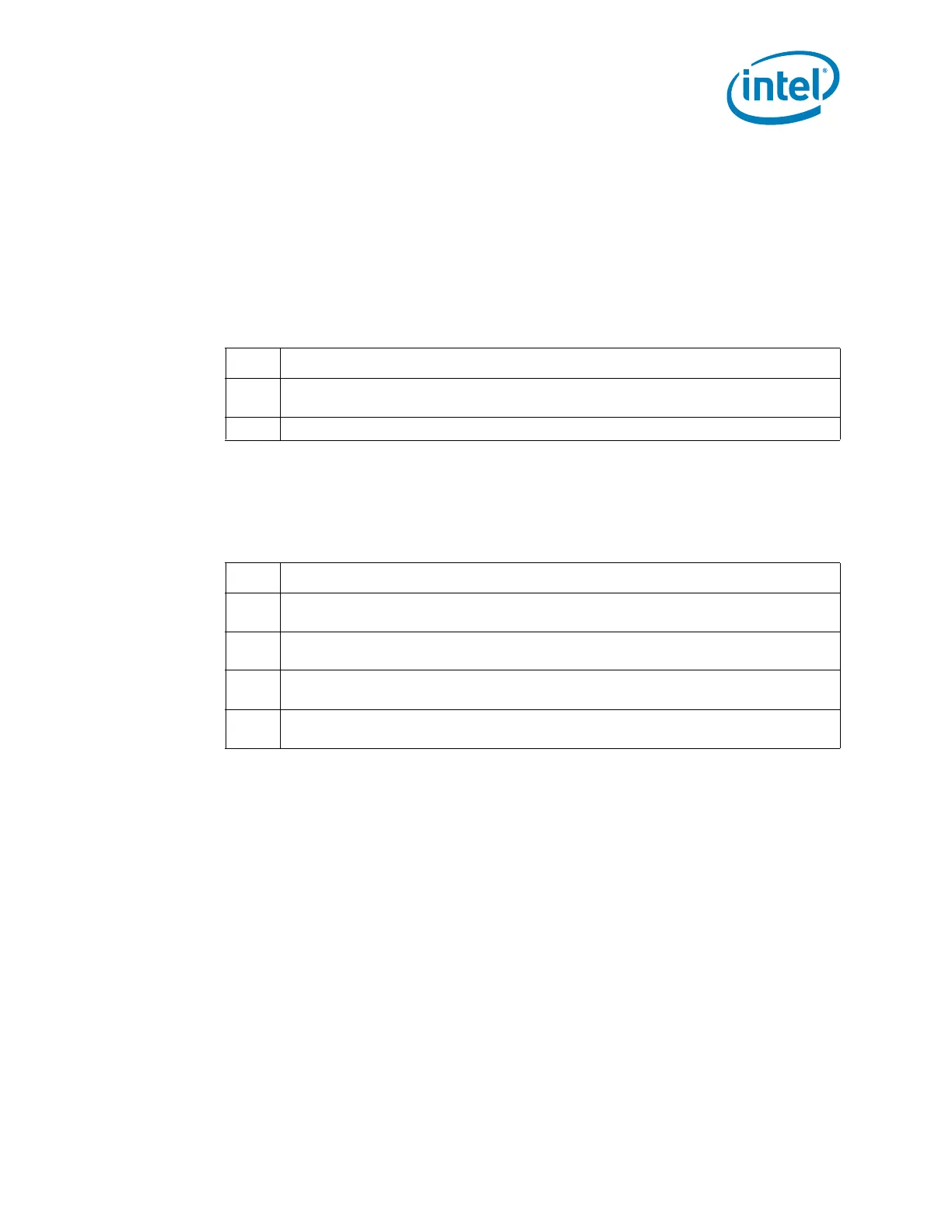

Bit Description

15:12

I/O Limit Address Limit bits[15:12] — R/W. I/O Base bits corresponding to address

lines 15:12 for 4-KB alignment. Bits 11:0 are assumed to be padded to FFFh.

11:8

I/O Limit Address Capability (IOLC) — RO. Indicates that the bridge does not

support 32-bit I/O addressing.

7:4

I/O Base Address (IOBA) — R/W. I/O Base bits corresponding to address lines 15:12

for 4-KB alignment. Bits 11:0 are assumed to be padded to 000h.

3:0

I/O Base Address Capability (IOBC) — RO. Indicates that the bridge does not

support 32-bit I/O addressing.

Loading...

Loading...