Datasheet 435

Gigabit LAN Configuration Registers

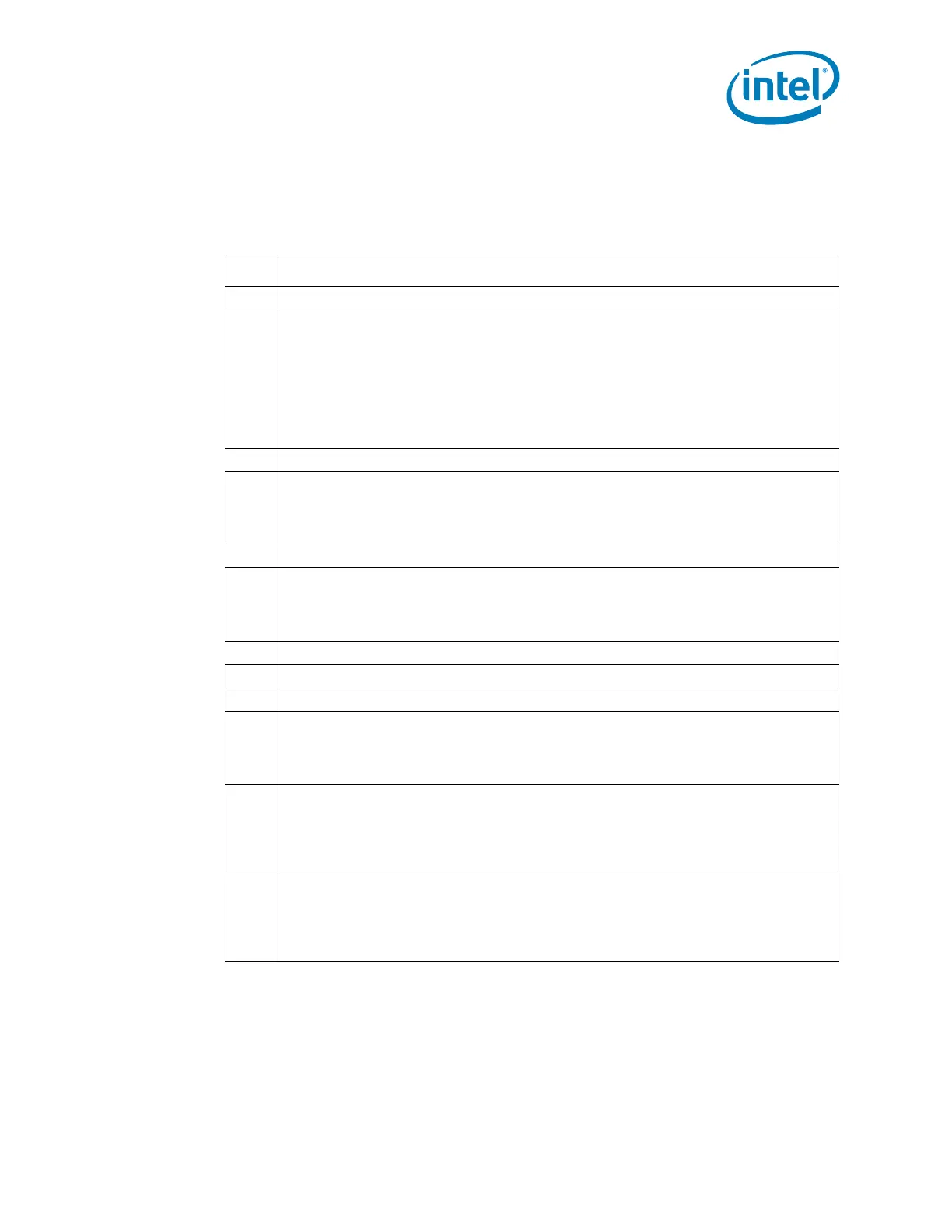

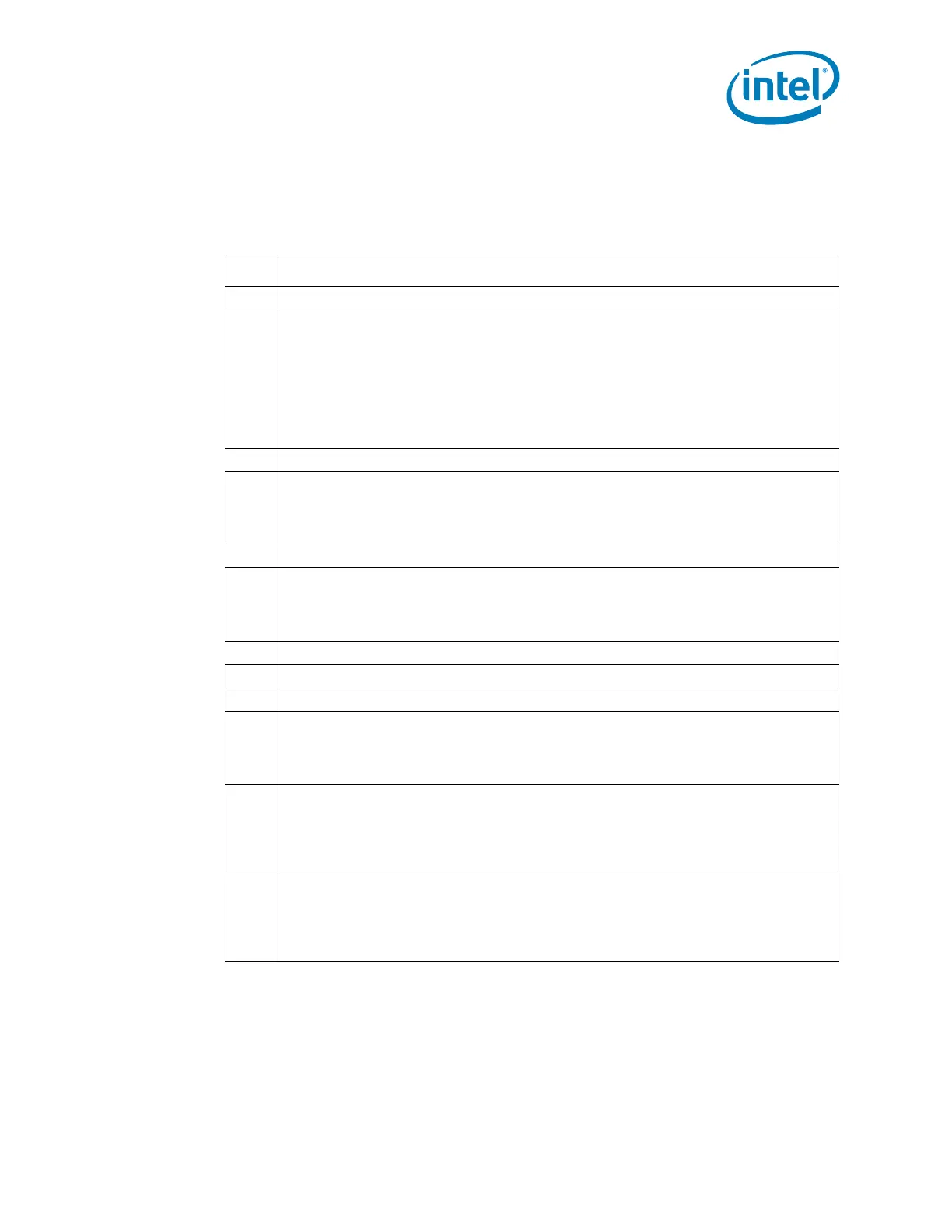

12.1.3 PCICMD—PCI Command Register

(Gigabit LAN—D25:F0)

Address Offset: 04h–05h Attribute: R/W, RO

Default Value: 0000h Size: 16 bits

Bit Description

15:11 Reserved

10

Interrupt Disable — R/W. This disables pin-based INTx# interrupts on enabled Hot-

Plug and power management events. This bit has no effect on MSI operation.

0 = Internal INTx# messages are generated if there is an interrupt for Hot-Plug or

power management and MSI is not enabled.

1 = Internal INTx# messages will not be generated.

This bit does not affect interrupt forwarding from devices connected to the root port.

Assert_INTx and Deassert_INTx messages will still be forwarded to the internal

interrupt controllers if this bit is set.

9 Fast Back to Back Enable (FBE) — RO. Hardwired to 0.

8

SERR# Enable (SEE) — R/W.

0 = Disable

1 = Enables the Gb LAN controller to generate an SERR# message when PSTS.SSE is

set.

7 Wait Cycle Control (WCC) — RO. Hardwired to 0.

6

Parity Error Response (PER) — R/W.

0 = Disable.

1 = Indicates that the device is capable of reporting parity errors as a master on the

backbone.

5 Palette Snoop Enable (PSE) — RO. Hardwired to 0.

4 Postable Memory Write Enable (PMWE) — RO. Hardwired to 0.

3 Special Cycle Enable (SCE) — RO. Hardwired to 0.

2

Bus Master Enable (BME) — R/W.

0 = Disable. All cycles from the device are master aborted

1 = Enable. Allows the root port to forward cycles onto the backbone from a Gigabit

LAN* device.

1

Memory Space Enable (MSE) — R/W.

0 = Disable. Memory cycles within the range specified by the memory base and limit

registers are master aborted on the backbone.

1 = Enable. Allows memory cycles within the range specified by the memory base and

limit registers can be forwarded to the Gigabit LAN device.

0

I/O Space Enable (IOSE) — R/W. This bit controls access to the I/O space registers.

0 = Disable. I/O cycles within the range specified by the I/O base and limit registers

are master aborted on the backbone.

1 = Enable. Allows I/O cycles within the range specified by the I/O base and limit

registers can be forwarded to the Gigabit LAN device.

Loading...

Loading...