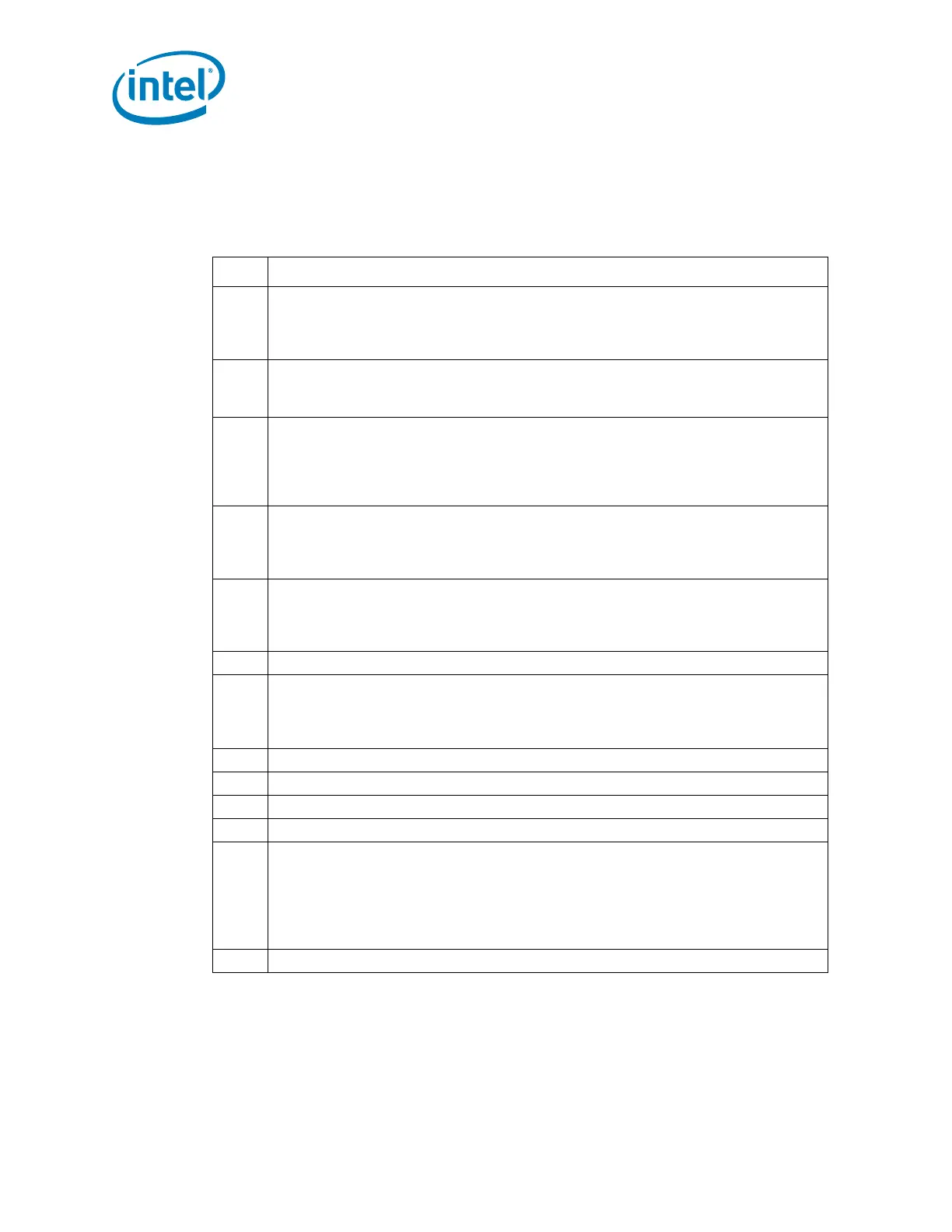

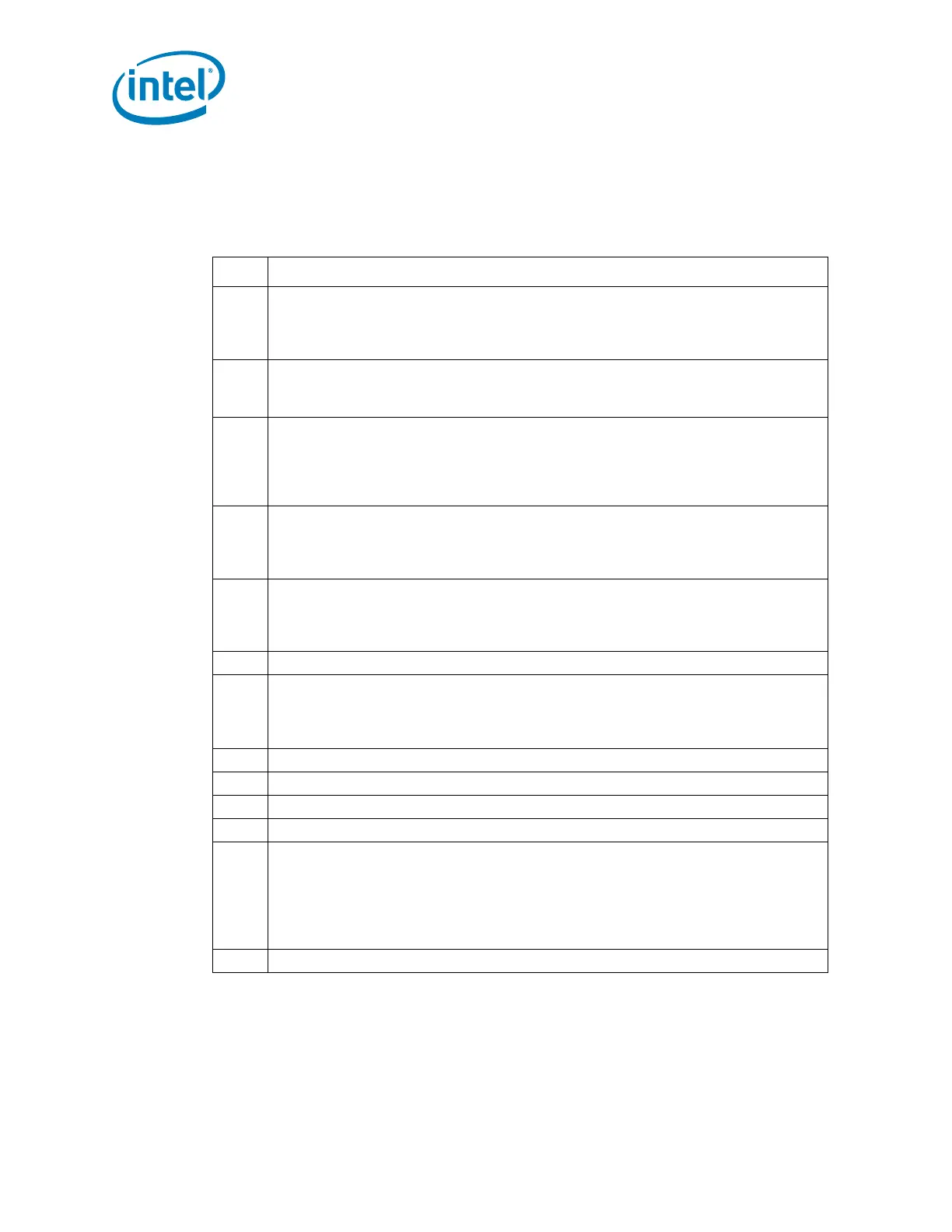

Gigabit LAN Configuration Registers

436 Datasheet

12.1.4 PCISTS—PCI Status Register

(Gigabit LAN—D25:F0)

Address Offset: 06h–07h Attribute: R/WC, RO

Default Value: 0010h Size: 16 bits

Bit Description

15

Detected Parity Error (DPE) — R/WC.

0 = No parity error detected.

1 = Set when the Gb LAN controller receives a command or data from the backbone

with a parity error. This is set even if PCIMD.PER (D25:F0, bit 6) is not set.

14

Signaled System Error (SSE) — R/WC.

0 = No system error signaled.

1 = Set when the Gb LAN controller signals a system error to the internal SERR# logic.

13

Received Master Abort (RMA) — R/WC.

0 = Root port has not received a completion with unsupported request status from the

backbone.

1 = Set when the GbE LAN controller receives a completion with unsupported request

status from the backbone.

12

Received Target Abort (RTA) — R/WC.

0 = Root port has not received a completion with completer abort from the backbone.

1 = Set when the Gb LAN controller receives a completion with completer abort from

the backbone.

11

Signaled Target Abort (STA) — R/WC.

0 = No target abort received.

1 = Set whenever the Gb LAN controller forwards a target abort received from the

downstream device onto the backbone.

10:9 DEVSEL# Timing Status (DEV_STS) — RO. Hardwired to ‘0’.

8

Master Data Parity Error Detected (DPED) — R/WC.

0 = No data parity error received.

1 = Set when the Gb LAN Controller receives a completion with a data parity error on

the backbone and PCIMD.PER (D25:F0, bit 6) is set.

7 Fast Back to Back Capable (FB2BC) — RO. Hardwired to ‘0’.

6Reserved

5 66 MHz Capable — RO. Hardwired to 0.

4 Capabilities List — RO. Hardwired to 1. Indicates the presence of a capabilities list.

3

Interrupt Status

— RO. Indicates status of Hot-Plug and power management

interrupts on the root port that result in INTx# message generation.

0 = Interrupt is deasserted.

1 = Interrupt is asserted.

This bit is not set if MSI is enabled. If MSI is not enabled, this bit is set regardless of the

state of PCICMD.Interrupt Disable bit (D25:F0:04h:bit 10).

2:0 Reserved

Loading...

Loading...