Gigabit LAN Configuration Registers

438 Datasheet

12.1.10 MBARA—Memory Base Address Register A

(Gigabit LAN—D25:F0)

Address Offset: 10h–13h Attribute: R/W, RO

Default Value: 00000000h Size: 32 bits

The internal CSR registers and memories are accessed as direct memory mapped

offsets from the base address register. SW may only access whole DWord at a time.

12.1.11 MBARB—Memory Base Address Register B

(Gigabit LAN—D25:F0)

Address Offset: 14h–17h Attribute: R/W, RO

Default Value: 00000000h Size: 32 bits

The internal registers that are used to access the LAN Space in the External FLASH

device. Access to these registers are direct memory mapped offsets from the base

address register. Software may only access a DWord at a time.

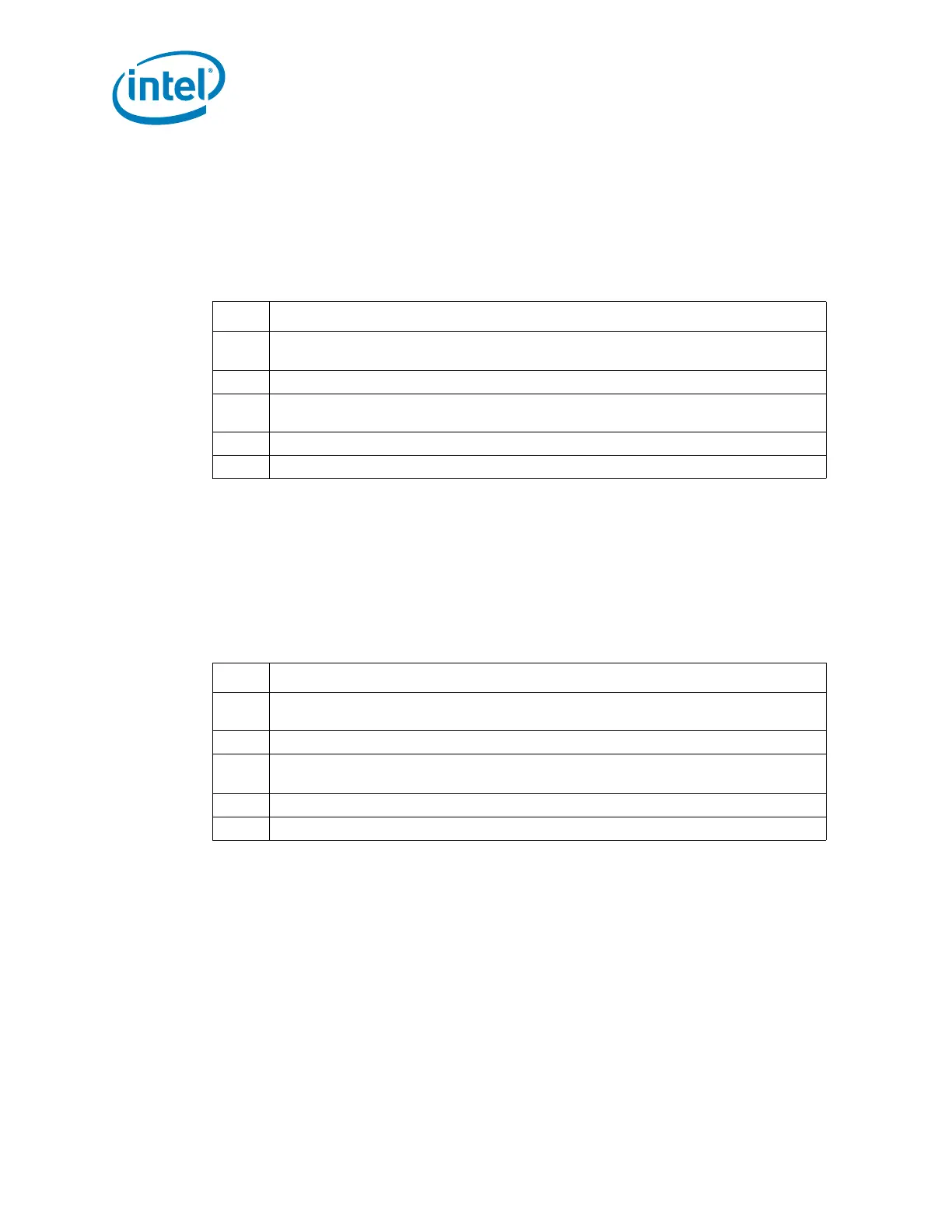

Bit Description

31:17

Base Address (BA) — R/W. Software programs this field with the base address of

this region.

16:4 Memory Size (MSIZE) — R/W. Memory size is 128 KB.

3

Prefetchable Memory (PM) — RO. The GbE LAN controller does not implement

prefetchable memory.

2:1 Memory Type (MT) — RO. Set to 00b indicating a 32 bit BAR.

0 Memory / IO Space (MIOS) — RO. Set to 0 indicating a Memory Space BAR.

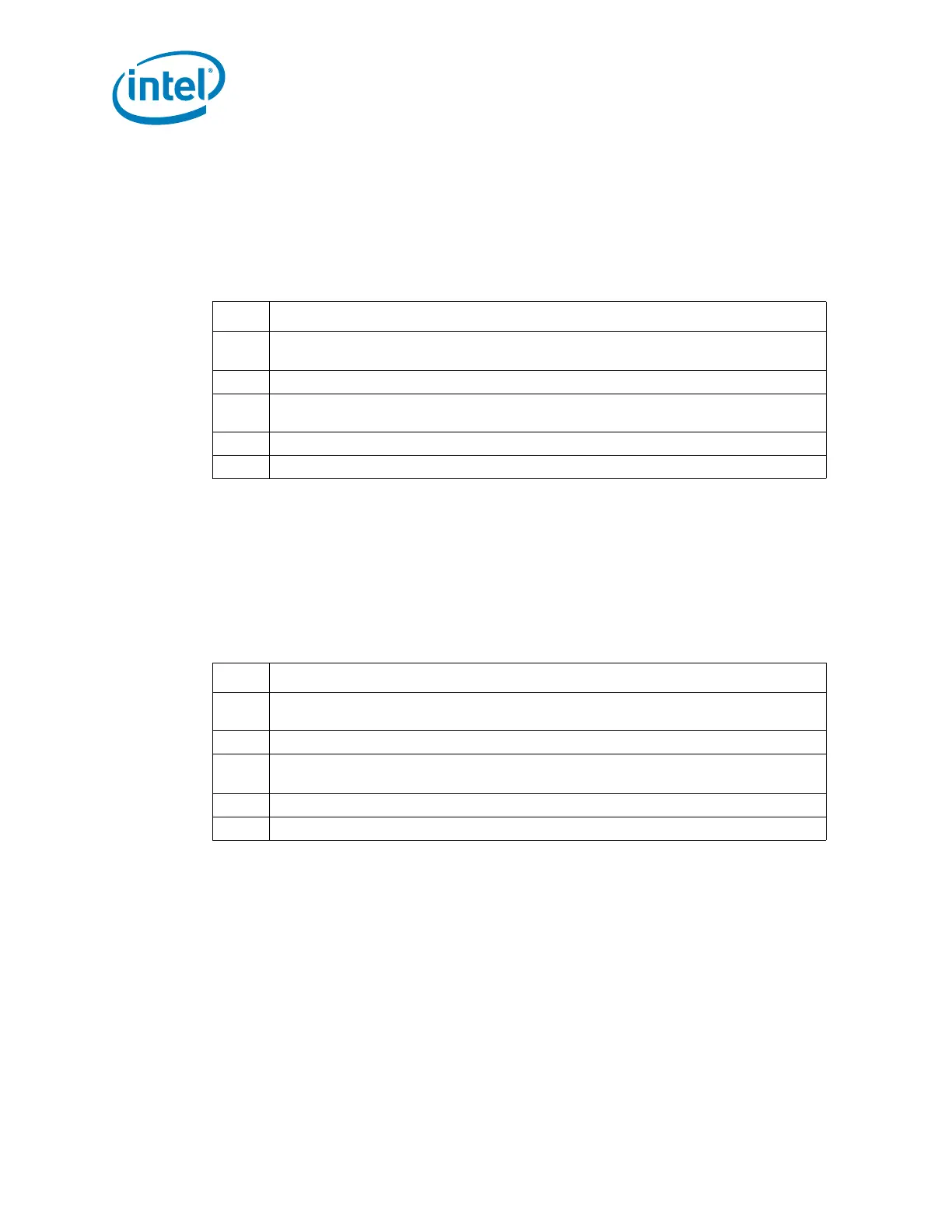

Bit Description

31:12

Base Address (BA) — R/W. Software programs this field with the base address of

this region.

11:4 Memory Size (MSIZE) — R/W. Memory size is 4 KB.

3

Prefetchable Memory (PM) — RO. The Gb LAN controller does not implement

prefetchable memory.

2:1 Memory Type (MT) — RO. Set to 00b indicating a 32 bit BAR.

0 Memory / IO Space (MIOS) — RO. Set to 0 indicating a Memory Space BAR.

Loading...

Loading...