Datasheet 491

LPC Interface Bridge Registers (D31:F0)

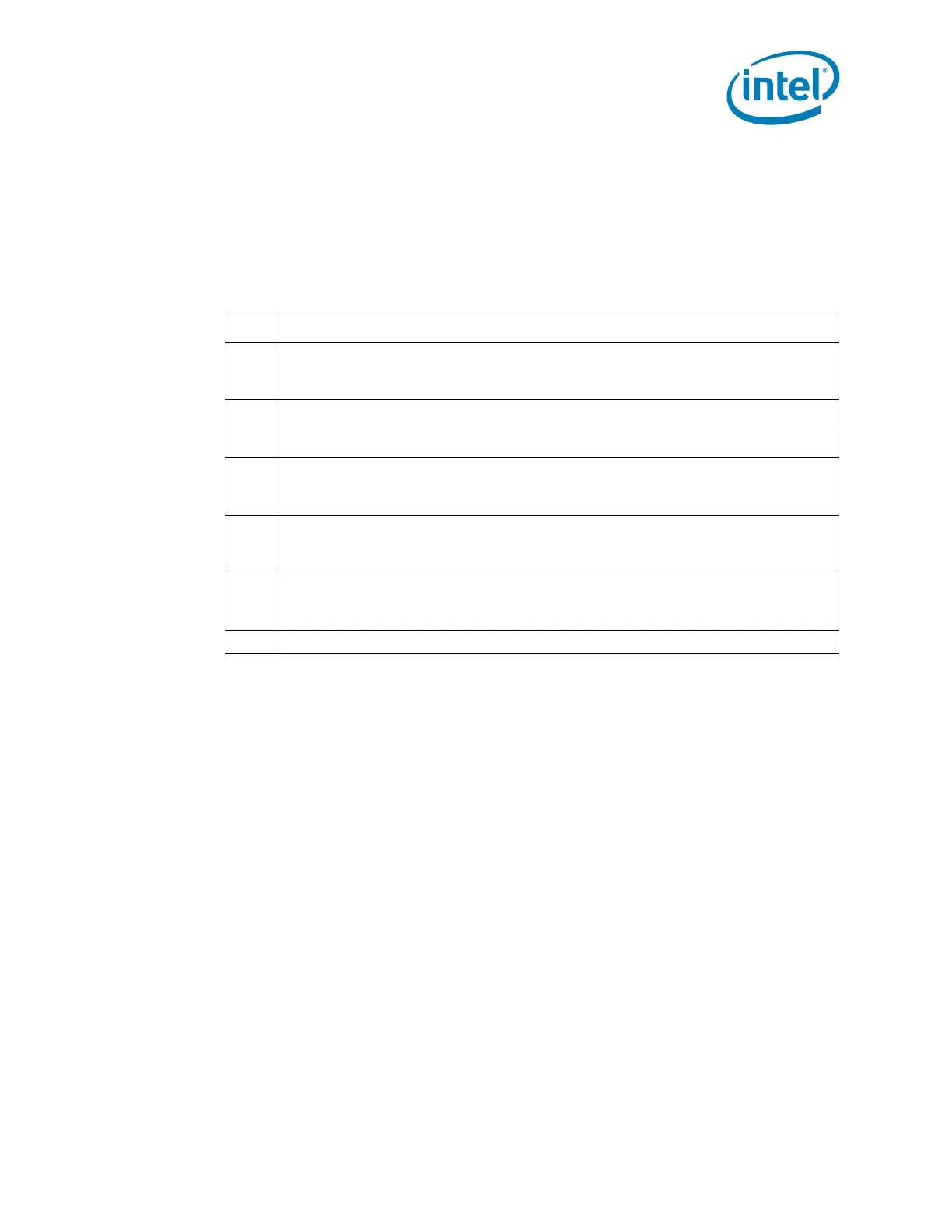

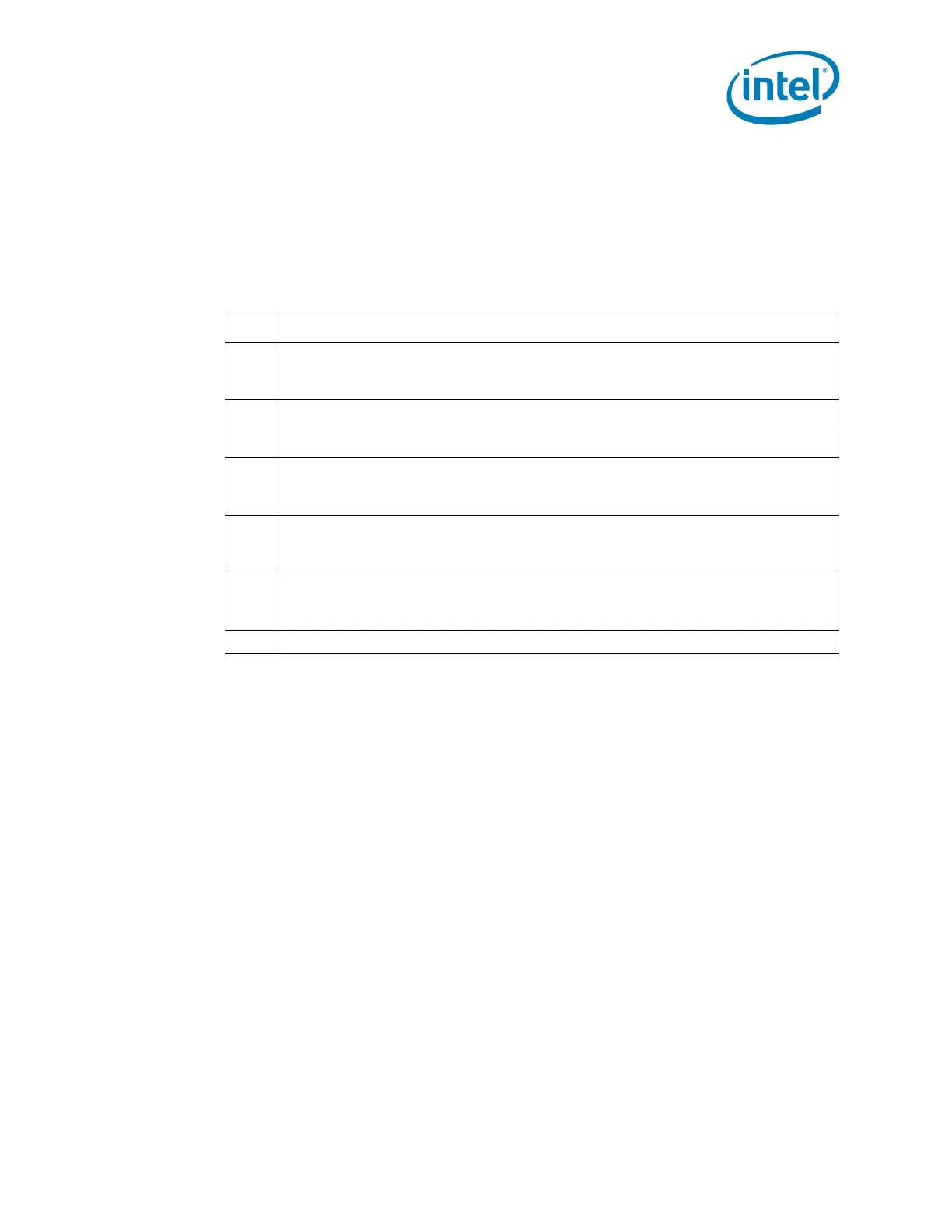

13.4.10 ELCR1—Master Controller Edge/Level Triggered Register

Offset Address: 4D0h Attribute: R/W

Default Value: 00h Size: 8 bits

In edge mode, (bit[x] = 0), the interrupt is recognized by a low to high transition. In

level mode (bit[x] = 1), the interrupt is recognized by a high level. The cascade

channel, IRQ2, the heart beat timer (IRQ0), and the keyboard controller (IRQ1),

cannot be put into level mode.

Bit Description

7

IRQ7 ECL — R/W.

0 = Edge

1 = Level

6

IRQ6 ECL — R/W.

0 = Edge

1 = Level.

5

IRQ5 ECL — R/W.

0 = Edge

1 = Level

4

IRQ4 ECL — R/W.

0 = Edge

1 = Level

3

IRQ3 ECL — R/W.

0 = Edge

1 = Level

2:0 Reserved. Must be 0.

Loading...

Loading...