Datasheet 583

SATA Controller Registers (D31:F2)

14.3 Serial ATA Index/Data Pair Superset Registers

All of these I/O registers are in the core well. They are exposed only when SCC is 01h

(that is, IDE programming interface).

These are Index/Data Pair registers that are used to access the SerialATA superset

registers (SerialATA Status (PxSSTS), SerialATA Control (PxSCTL) and SerialATA Error

(PxSERR)). The I/O space for these registers is allocated through SIDPBA. Locations

with offset from 08h to 0Fh are reserved for future expansion. Software-write

operations to the reserved locations will have no effect while software-read operations

to the reserved locations will return 0.

14.3.1 SINDX—Serial ATA Index (D31:F2)

Address Offset: SIDPBA + 00h Attribute: R/W

Default Value: 00000000h Size: 32 bits

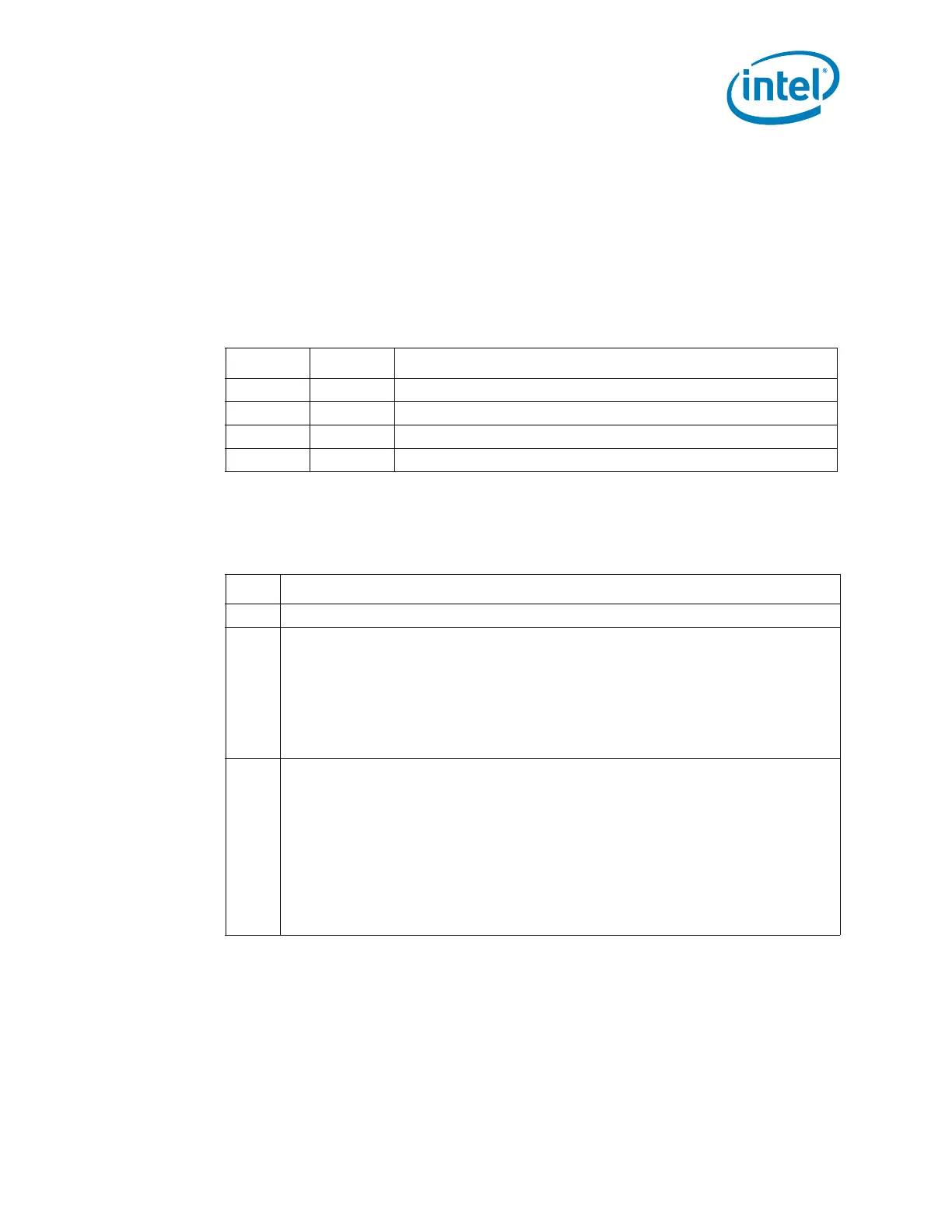

Offset Mnemonic Register

00h–03h SINDEX Serial ATA Index

04h–07h SDATA Serial ATA Data

08h–0Ch — Reserved

0Ch–0Fh — Reserved

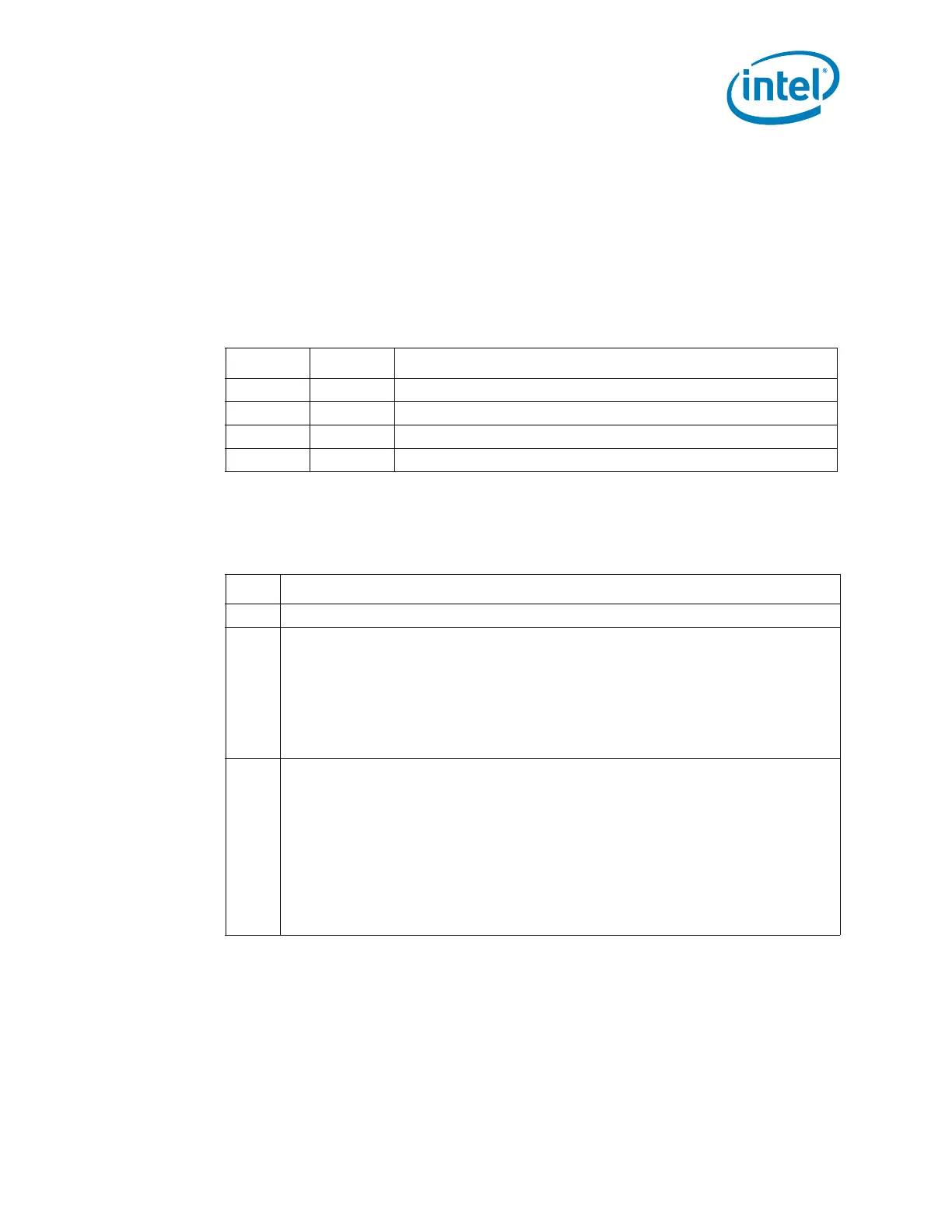

Bit Description

31:16 Reserved

15.8

Port Index (PIDX)—R/W. This Index field is used to specify the port of the SATA

controller at which the port-specific SSTS, SCTL, and SERR registers are located.

00h = Primary Master (Port 0)

01h = Primary Slave (Port 2)

02h = Secondary Master (Port 1)

03h = Secondary Slave (Port 3)

All other values are Reserved.

7:0

Register Index (RIDX)—R/W. This index field is used to specify one out of three

registers currently being indexed into. These three registers are the Serial ATA superset

SStatus, SControl and SError memory registers and are port specific, hence for this

SATA controller, there are four sets of these registers. Refer to Section 14.4.2.10,

Section 14.4.2.11, and Section 14.4.2.12 for definitions of the SStatus, SControl and

SError registers.

00h = SSTS

01h = SCTL

02h = SERR

All other values are Reserved.

Loading...

Loading...