Integrated Intel

®

High Definition Audio Controller Registers

686 Datasheet

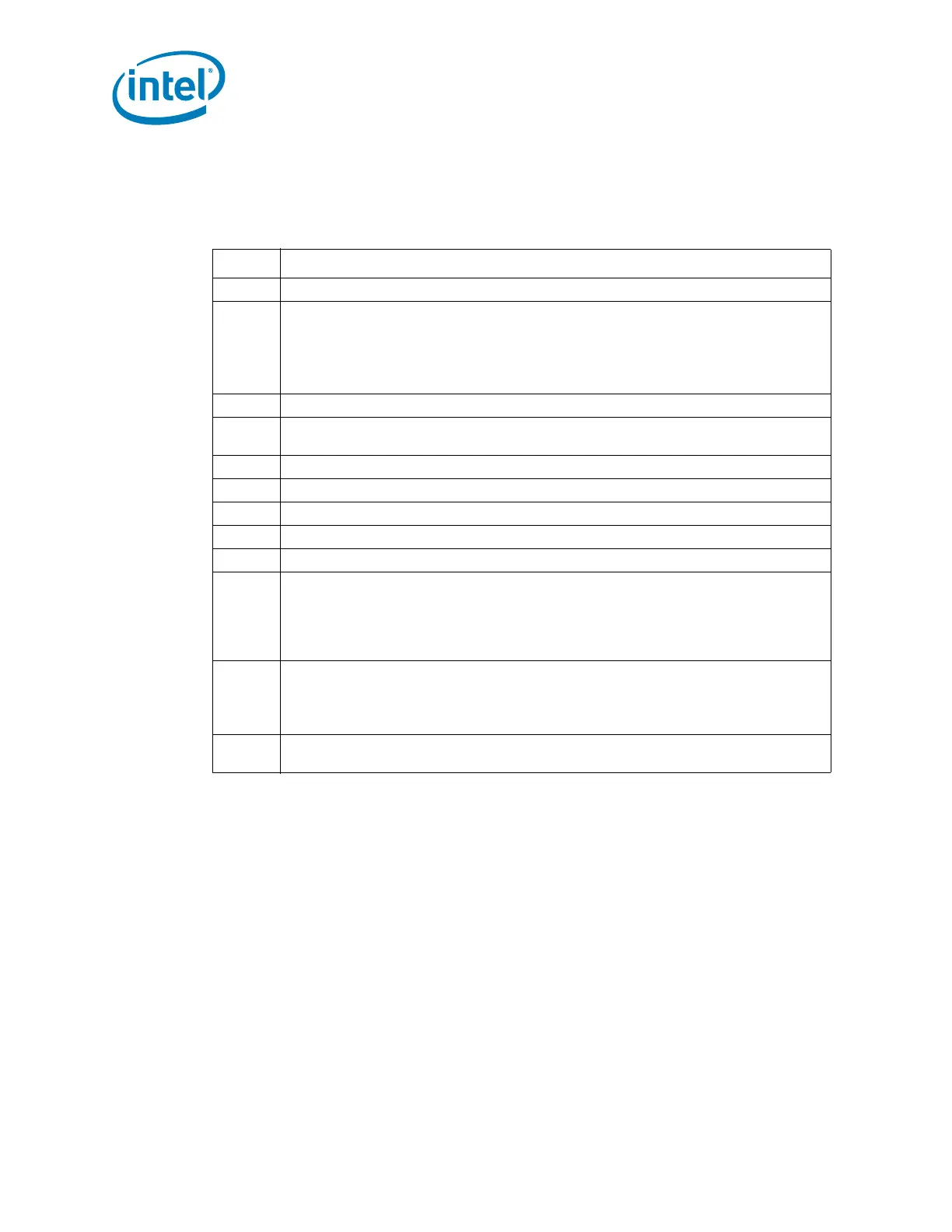

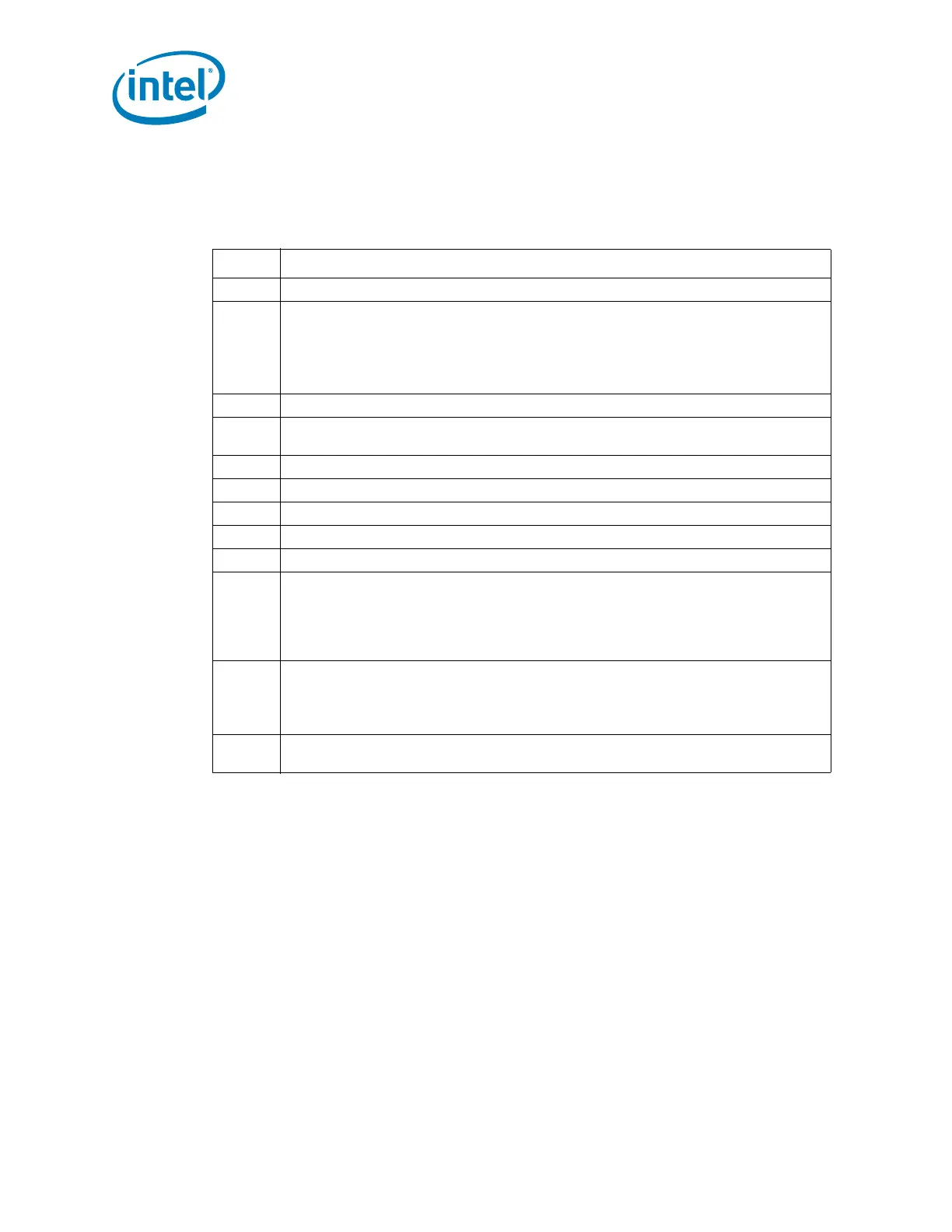

17.1.1.3 PCICMD—PCI Command Register

(Intel

®

High Definition Audio Controller—D27:F0)

Offset Address: 04h–05h Attribute: R/W, RO

Default Value: 0000h Size: 16 bits

Bit Description

15:11 Reserved

10

Interrupt Disable (ID) — R/W.

0= The INTx# signals may be asserted.

1= The Intel

®

High Definition Audio controller’s INTx# signal will be deasserted.

NOTE: This bit does not affect the generation of MSIs.

9 Fast Back to Back Enable (FBE) — RO. Not implemented. Hardwired to 0.

8

SERR# Enable (SERR_EN) — R/W. SERR# is not generated by the PCH Intel

®

High

Definition Audio Controller.

7 Wait Cycle Control (WCC) — RO. Not implemented. Hardwired to 0.

6 Parity Error Response (PER) — R/W. Not implemented.

5 VGA Palette Snoop (VPS). Not implemented. Hardwired to 0.

4 Memory Write and Invalidate Enable (MWIE) — RO. Not implemented. Hardwired to 0.

3 Special Cycle Enable (SCE). Not implemented. Hardwired to 0.

2

Bus Master Enable (BME) — R/W. Controls standard PCI Express* bus mastering

capabilities for Memory and I/O, reads and writes. Note that this bit also controls MSI

generation since MSI’s are essentially Memory writes.

0 = Disable

1 = Enable

1

Memory Space Enable (MSE) — R/W. Enables memory space addresses to the

Intel

®

High Definition Audio controller.

0 = Disable

1 = Enable

0

I/O Space Enable (IOSE)—RO. Hardwired to 0 since the Intel

®

High Definition Audio

controller does not implement I/O space.

Loading...

Loading...