Integrated Intel

®

High Definition Audio Controller Registers

688 Datasheet

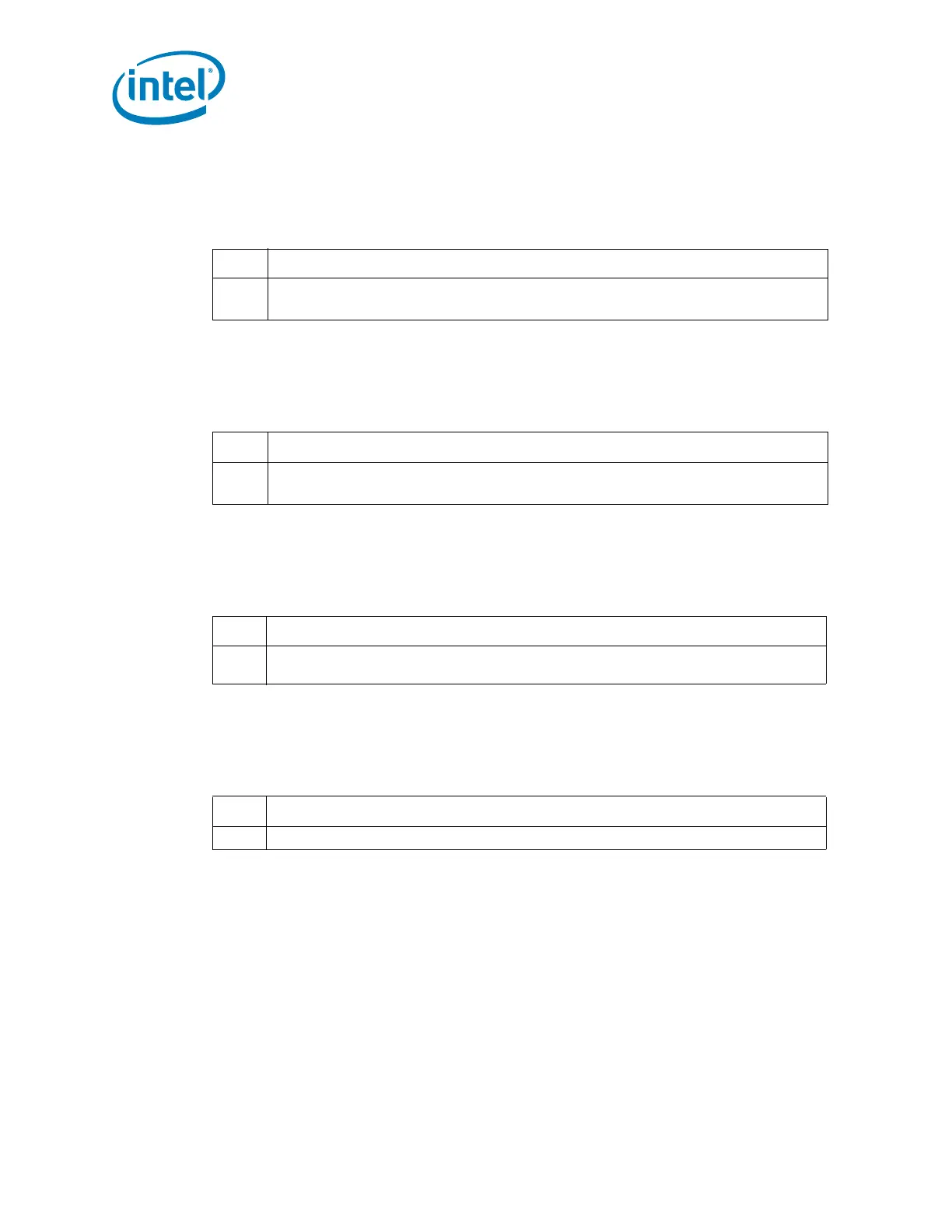

17.1.1.7 SCC—Sub Class Code Register

(Intel

®

High Definition Audio Controller—D27:F0)

Address Offset: 0Ah Attribute: RO

Default Value: 03h Size: 8 bits

17.1.1.8 BCC—Base Class Code Register

(Intel

®

High Definition Audio Controller—D27:F0)

Address Offset: 0Bh Attribute: RO

Default Value: 04h Size: 8 bits

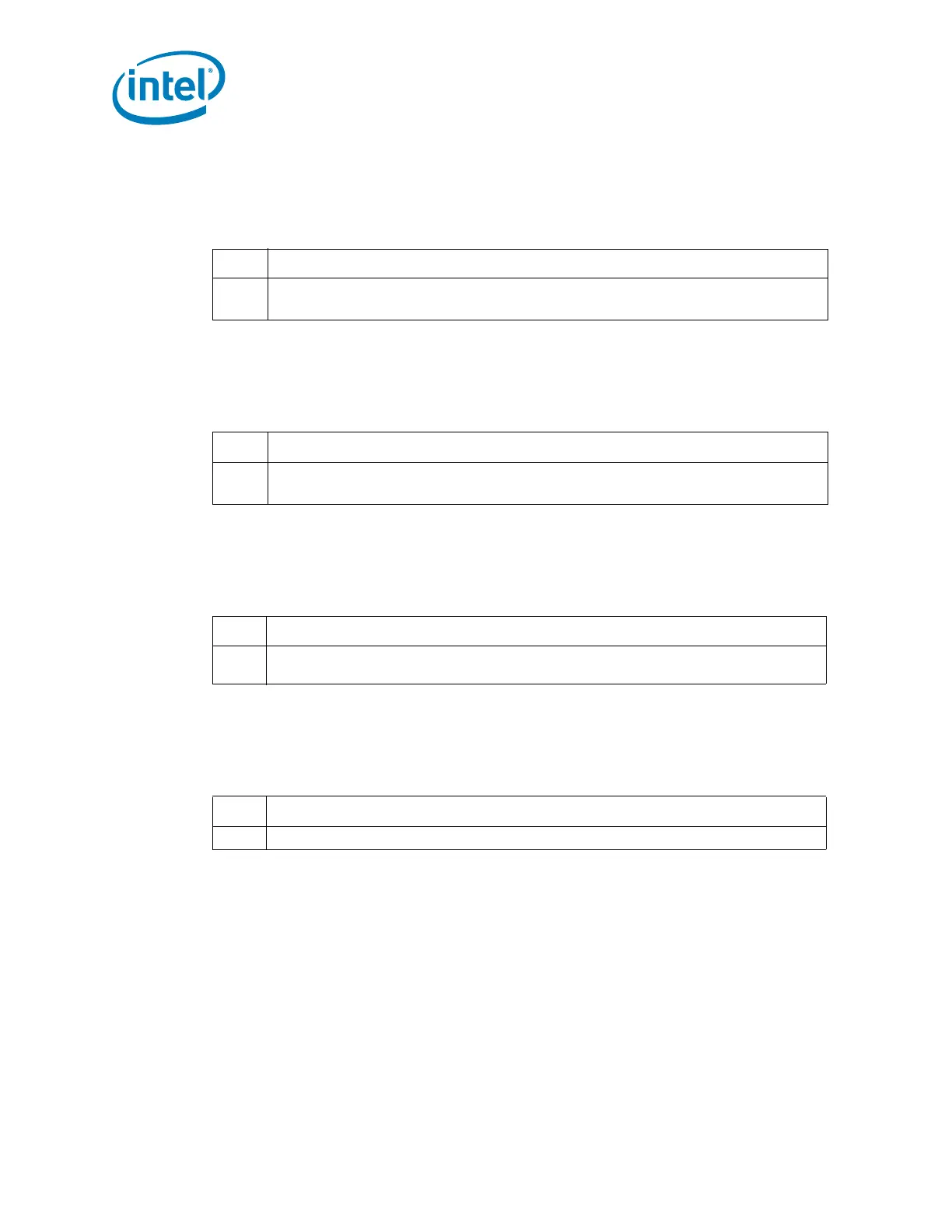

17.1.1.9 CLS—Cache Line Size Register

(Intel

®

High Definition Audio Controller—D27:F0)

Address Offset: 0Ch Attribute: R/W

Default Value: 00h Size: 8 bits

17.1.1.10 LT—Latency Timer Register

(Intel

®

High Definition Audio Controller—D27:F0)

Address Offset: 0Dh Attribute: RO

Default Value: 00h Size: 8 bits

Bit Description

7:0

Sub Class Code (SCC) — RO.

03h = Audio Device

Bit Description

7:0

Base Class Code (BCC) — RO.

04h = Multimedia device

Bit Description

7:0

Cache Line Size — R/W. Implemented as R/W register, but has no functional impact to

the PCH

Bit Description

7:0 Latency Timer — RO. Hardwired to 00

Loading...

Loading...