Integrated Intel

®

High Definition Audio Controller Registers

700 Datasheet

17.1.1.37 PVCCAP1—Port VC Capability Register 1

(Intel

®

High Definition Audio Controller—D27:F0)

Address Offset: 104h–107h Attribute: RO

Default Value: 00000001h Size: 32 bits

17.1.1.38 PVCCAP2 — Port VC Capability Register 2

(Intel

®

High Definition Audio Controller—D27:F0)

Address Offset: 108h–10Bh Attribute: RO

Default Value: 00000000h Size: 32 bits

17.1.1.39 PVCCTL — Port VC Control Register

(Intel

®

High Definition Audio Controller—D27:F0)

Address Offset: 10Ch–10Dh Attribute: RO

Default Value: 0000h Size: 16 bits

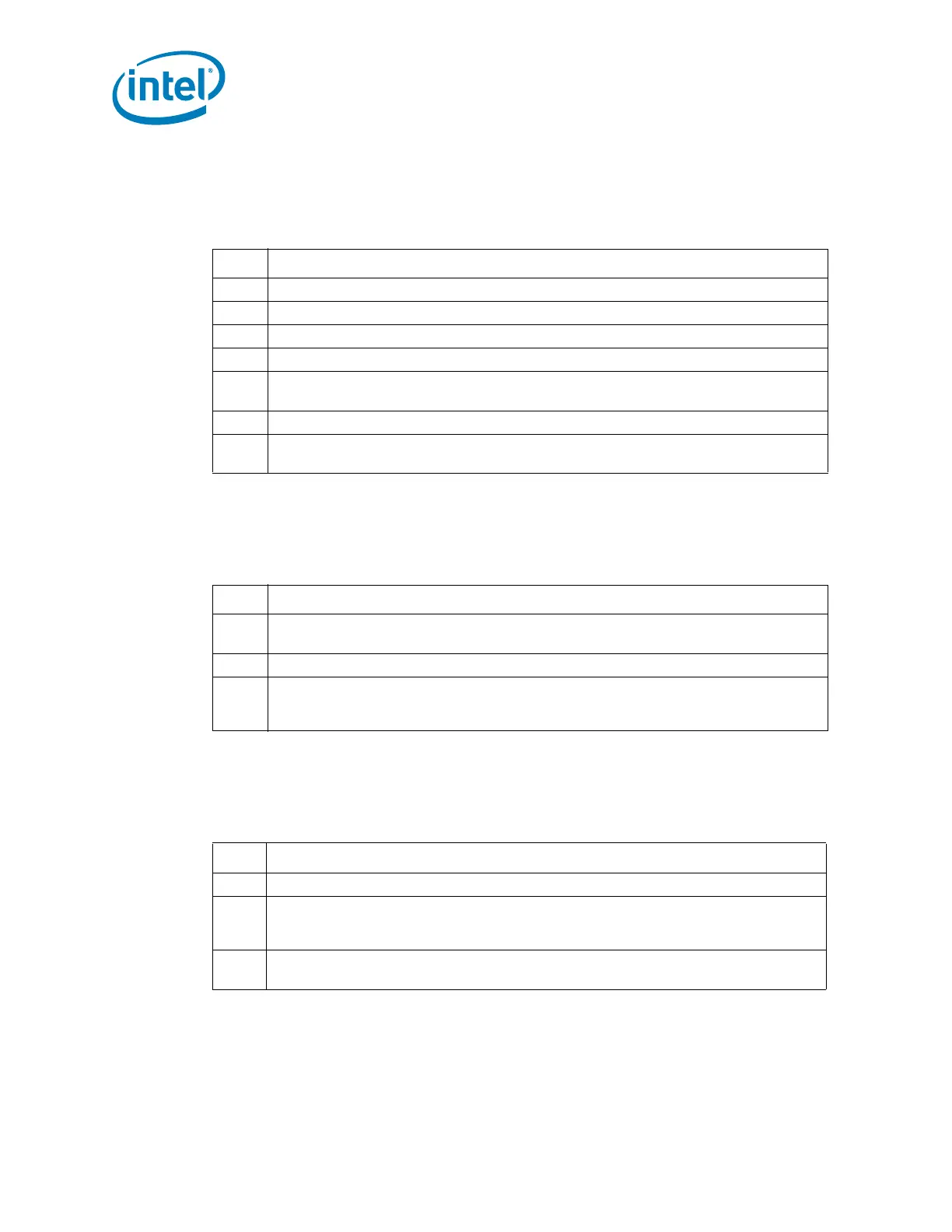

Bit Description

31:12 Reserved.

11:10 Port Arbitration Table Entry Size — RO. Hardwired to 0 since this is an endpoint device.

9:8 Reference Clock — RO. Hardwired to 0 since this is an endpoint device.

7Reserved.

6:4

Low Priority Extended VC Count — RO. Hardwired to 0. Indicates that only VC0 belongs

to the low priority VC group.

3Reserved.

2:0

Extended VC Count — RO. Hardwired to 001b. Indicates that 1 extended VC (in

addition to VC0) is supported by the Intel

®

High Definition Audio controller.

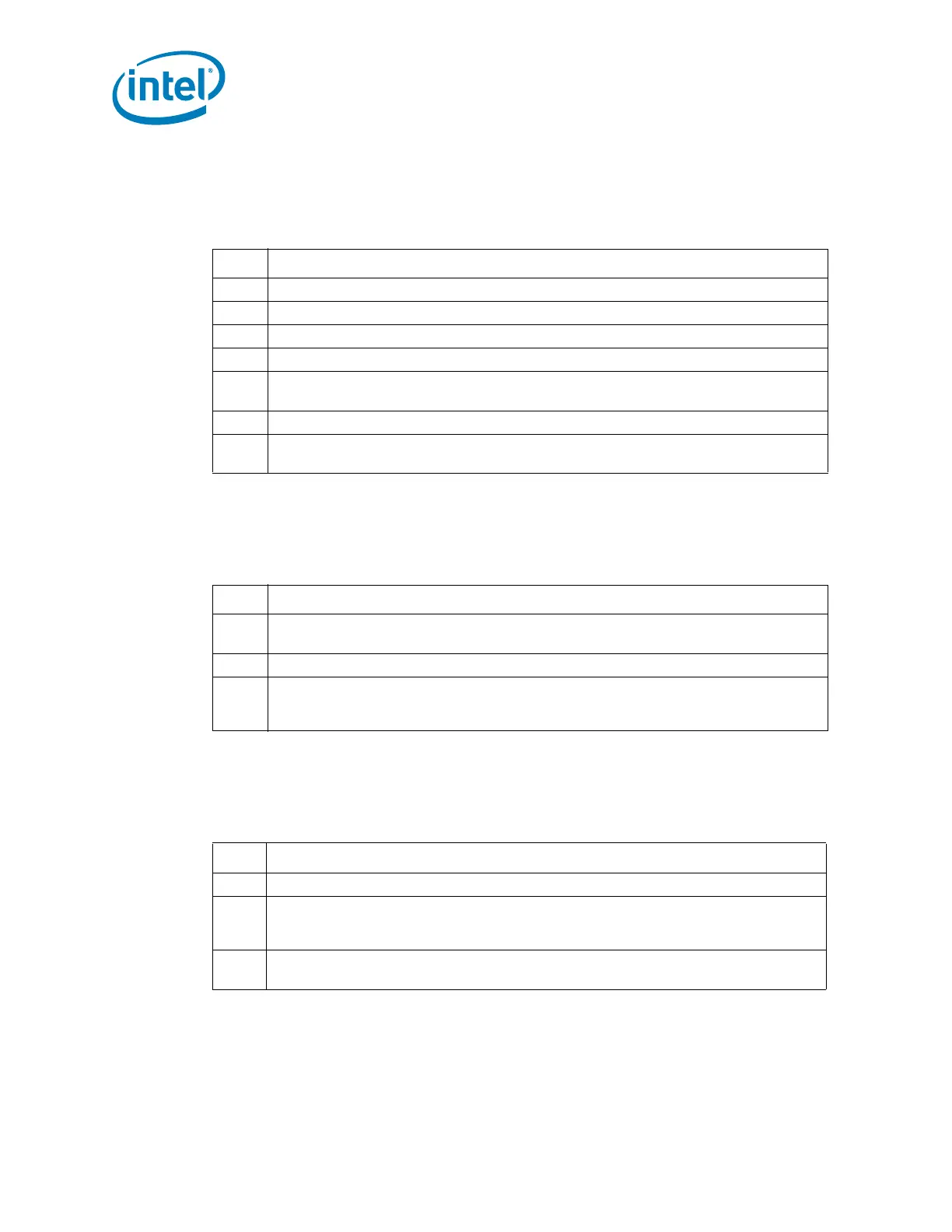

Bit Description

31:24

VC Arbitration Table Offset — RO. Hardwired to 0 indicating that a VC arbitration table

is not present.

23:8 Reserved.

7:0

VC Arbitration Capability — RO. Hardwired to 0. These bits are not applicable since the

Intel

®

High Definition Audio controller reports a 0 in the Low Priority Extended VC

Count bits in the PVCCAP1 register.

Bit Description

15:4 Reserved.

3:1

VC Arbitration Select — RO. Hardwired to 0. Normally these bits are R/W. However,

these bits are not applicable since the Intel

®

High Definition Audio controller reports a

0 in the Low Priority Extended VC Count bits in the PVCCAP1 register.

0

Load VC Arbitration Table — RO. Hardwired to 0 since an arbitration table is not

present.

Loading...

Loading...