Datasheet 703

Integrated Intel

®

High Definition Audio Controller Registers

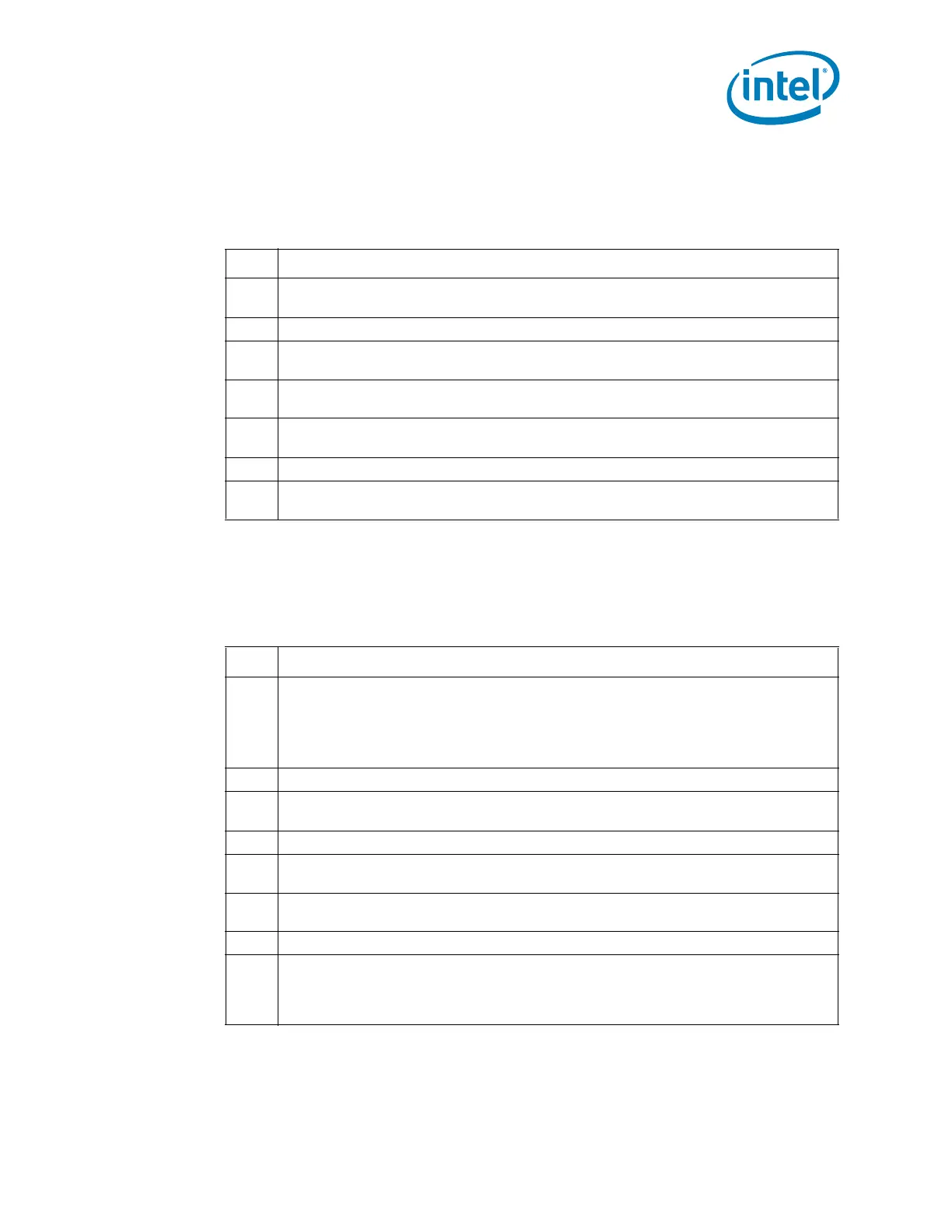

17.1.1.44 VCiCAP—VCi Resource Capability Register

(Intel

®

High Definition Audio Controller—D27:F0)

Address Offset: 11Ch–11Fh Attribute: RO

Default Value: 00000000h Size: 32 bits

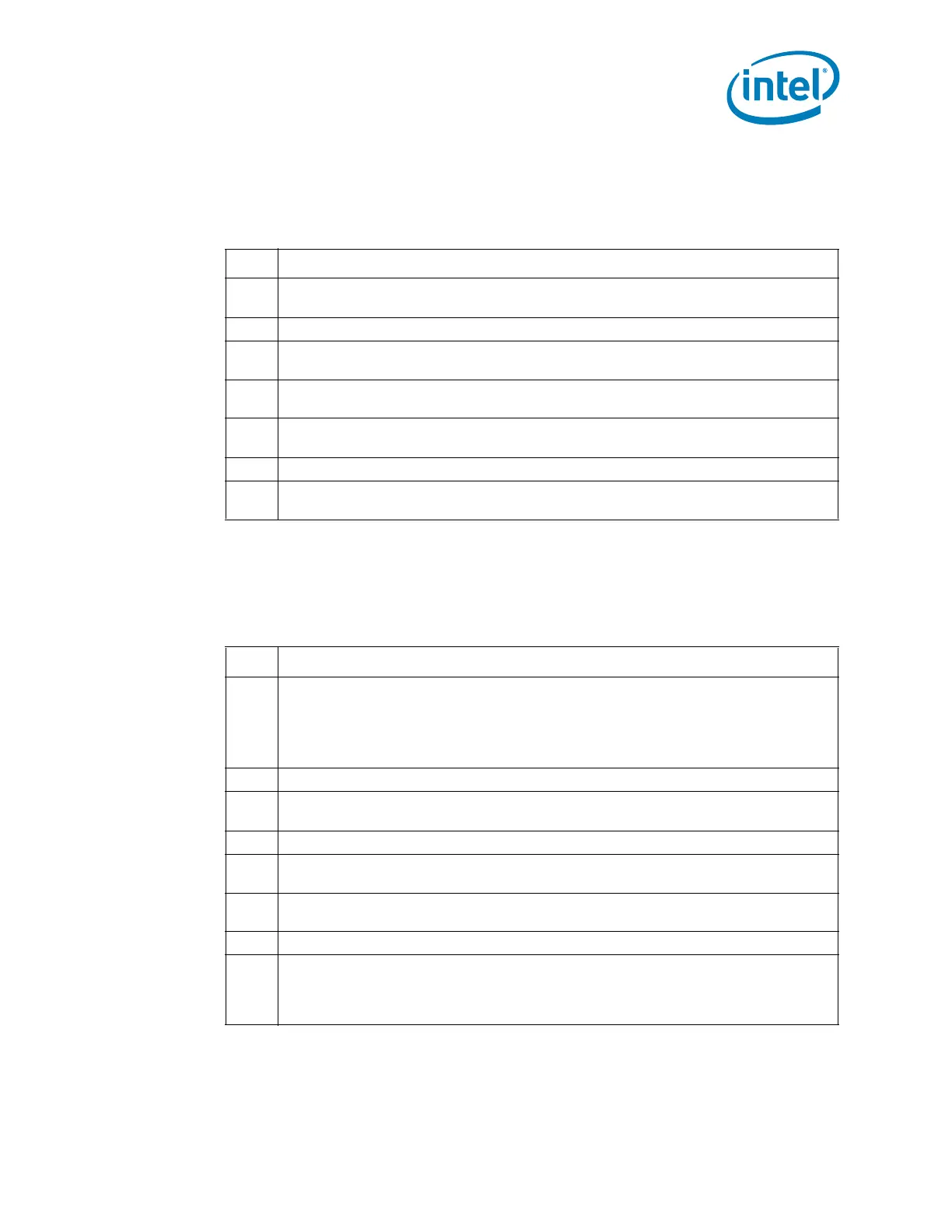

17.1.1.45 VCiCTL—VCi Resource Control Register

(Intel

®

High Definition Audio Controller—D27:F0)

Address Offset: 120h–123h Attribute: R/W, RO

Default Value: 00000000h Size: 32 bits

Function Level Reset: No

Bit Description

31:24

Port Arbitration Table Offset — RO. Hardwired to 0 since this field is not valid for

endpoint devices.

23 Reserved.

22:16

Maximum Time Slots — RO. Hardwired to 0 since this field is not valid for endpoint

devices.

15

Reject Snoop Transactions — RO. Hardwired to 0 since this field is not valid for endpoint

devices.

14

Advanced Packet Switching — RO. Hardwired to 0 since this field is not valid for

endpoint devices.

13:8 Reserved

7:0

Port Arbitration Capability — RO. Hardwired to 0 since this field is not valid for endpoint

devices.

Bit Description

31

VCi Enable — R/W.

0 = VCi is disabled

1 = VCi is enabled

NOTE: This bit is not reset on D3

HOT

to D0 transition; however, it is reset by PLTRST#.

30:27 Reserved.

26:24

VCi ID — R/W. This field assigns a VC ID to the VCi resource. This field is not used by

the PCH hardware, but it is R/W to avoid confusing software.

23:20 Reserved.

19:17

Port Arbitration Select — RO. Hardwired to 0 since this field is not valid for endpoint

devices.

16

Load Port Arbitration Table — RO. Hardwired to 0 since this field is not valid for endpoint

devices.

15:8 Reserved.

7:0

TC/VCi Map — R/W, RO. This field indicates the TCs that are mapped to the VCi

resource. Bit 0 is hardwired to 0 indicating that it cannot be mapped to VCi. Bits [7:1]

are implemented as R/W bits. This field is not used by the PCH hardware, but it is R/W

to avoid confusing software.

Loading...

Loading...