Integrated Intel

®

High Definition Audio Controller Registers

704 Datasheet

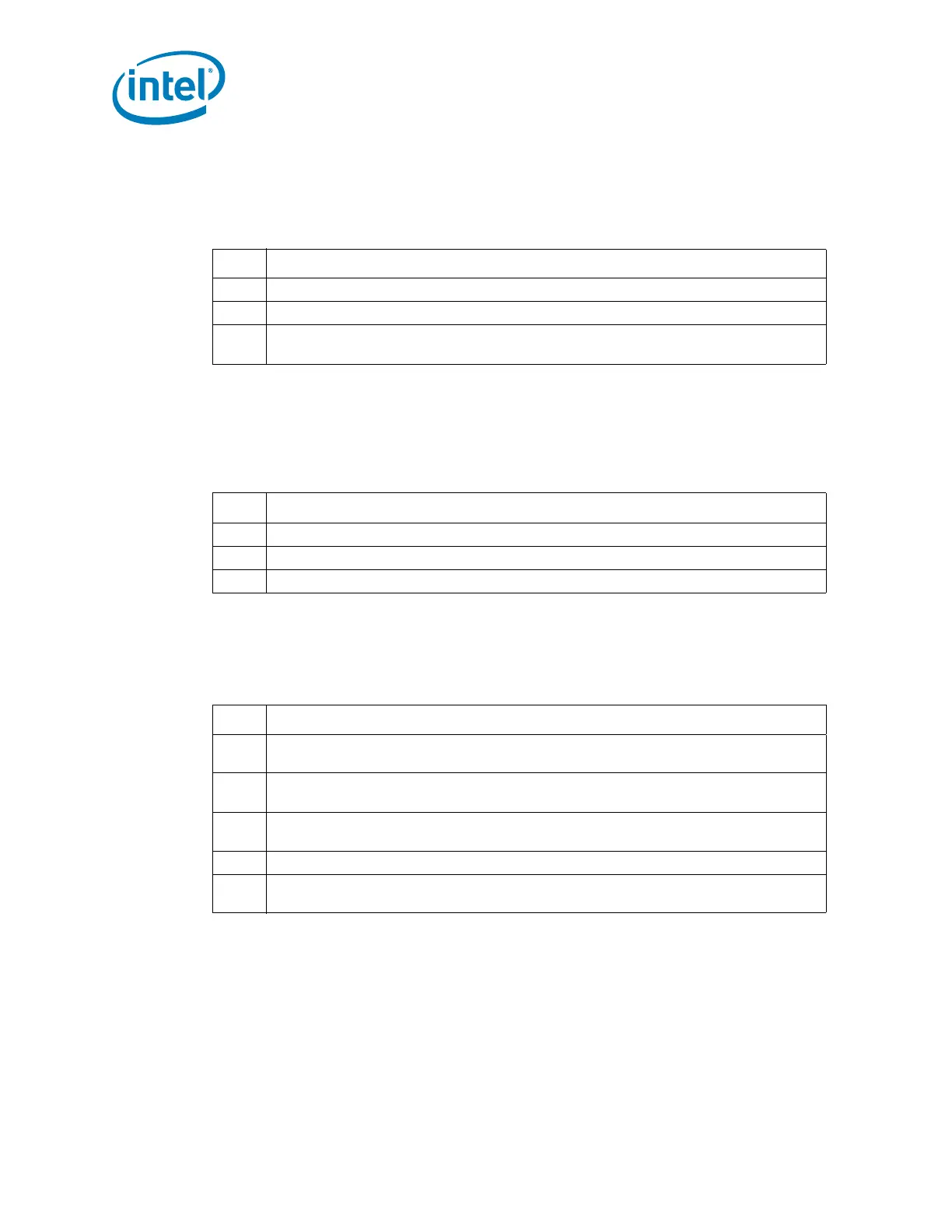

17.1.1.46 VCiSTS—VCi Resource Status Register

(Intel

®

High Definition Audio Controller—D27:F0)

Address Offset: 126h–127h Attribute: RO

Default Value: 0000h Size: 16 bits

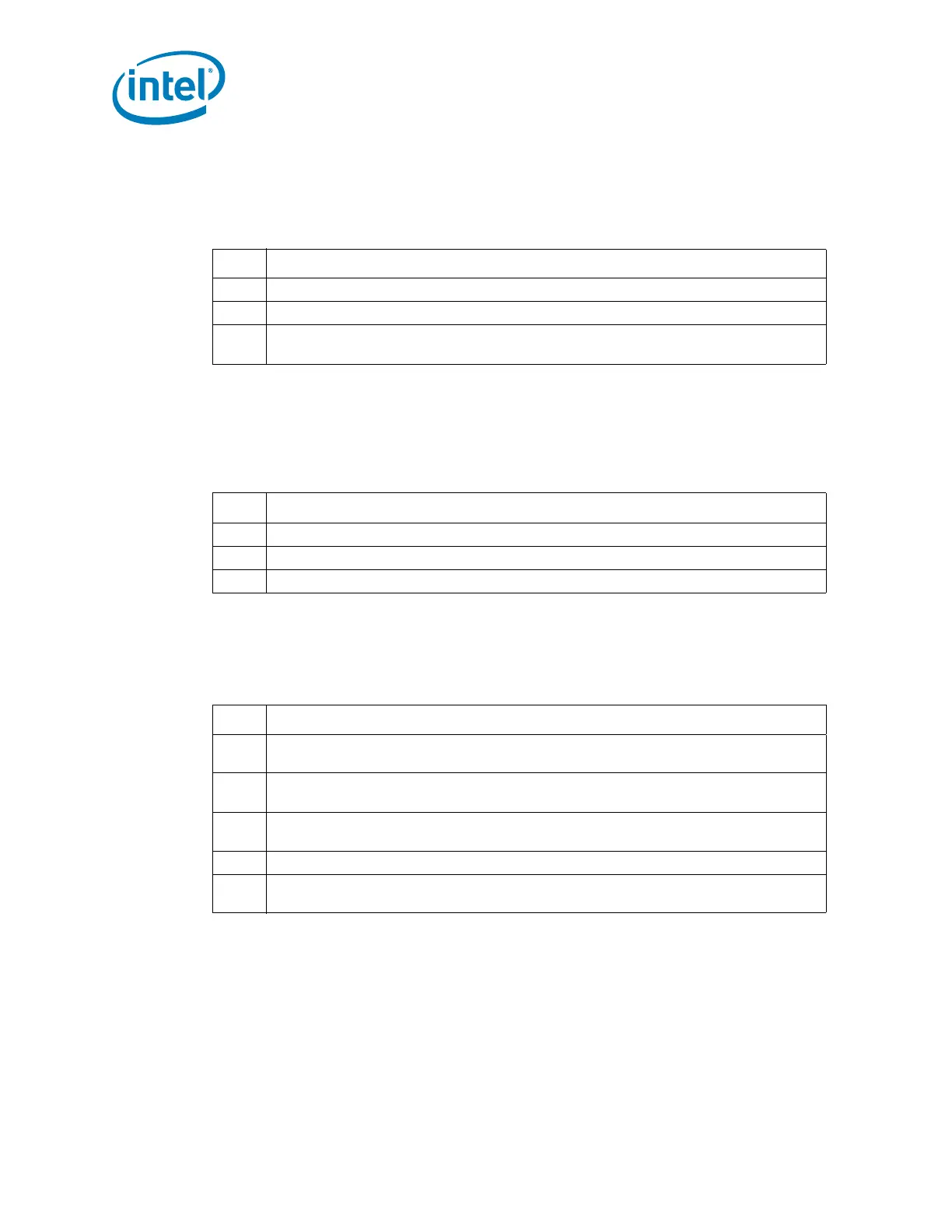

17.1.1.47 RCCAP—Root Complex Link Declaration Enhanced

Capability Header Register

(Intel

®

High Definition Audio Controller—D27:F0)

Address Offset: 130h Attribute: RO

Default Value: 00010005h Size: 32 bits

17.1.1.48 ESD—Element Self Description Register

(Intel

®

High Definition Audio Controller—D27:F0)

Address Offset: 134h–137h Attribute: RO

Default Value: 0F000100h Size: 32 bits

Bit Description

15:2 Reserved.

1 VCi Negotiation Pending — RO. Does not apply. Hardwired to 0.

0

Port Arbitration Table Status — RO. Hardwired to 0 since this field is not valid for

endpoint devices.

Bit Description

31:20 Next Capability Offset — RO. Hardwired to 0 indicating this is the last capability.

19:16 Capability Version — RO. Hardwired to 1h.

15:0 PCI Express* Extended Capability ID — RO. Hardwired to 0005h.

Bit Description

31:24

Port Number — RO. Hardwired to 0Fh indicating that the Intel

®

High Definition Audio

controller is assigned as Port #15d.

23:16

Component ID — RO. This field returns the value of the ESD.CID field of the chip

configuration section. ESD.CID is programmed by BIOS.

15:8

Number of Link Entries — RO. The Intel

®

High Definition Audio only connects to one

device, the PCH egress port. Therefore, this field reports a value of 1h.

7:4 Reserved.

3:0

Element Type (ELTYP) — RO. The Intel

®

High Definition Audio controller is an

integrated Root Complex Device. Therefore, the field reports a value of 0h.

Loading...

Loading...