Datasheet 723

Integrated Intel

®

High Definition Audio Controller Registers

17.1.2.31 IR—Immediate Response Register

(Intel

®

High Definition Audio Controller—D27:F0)

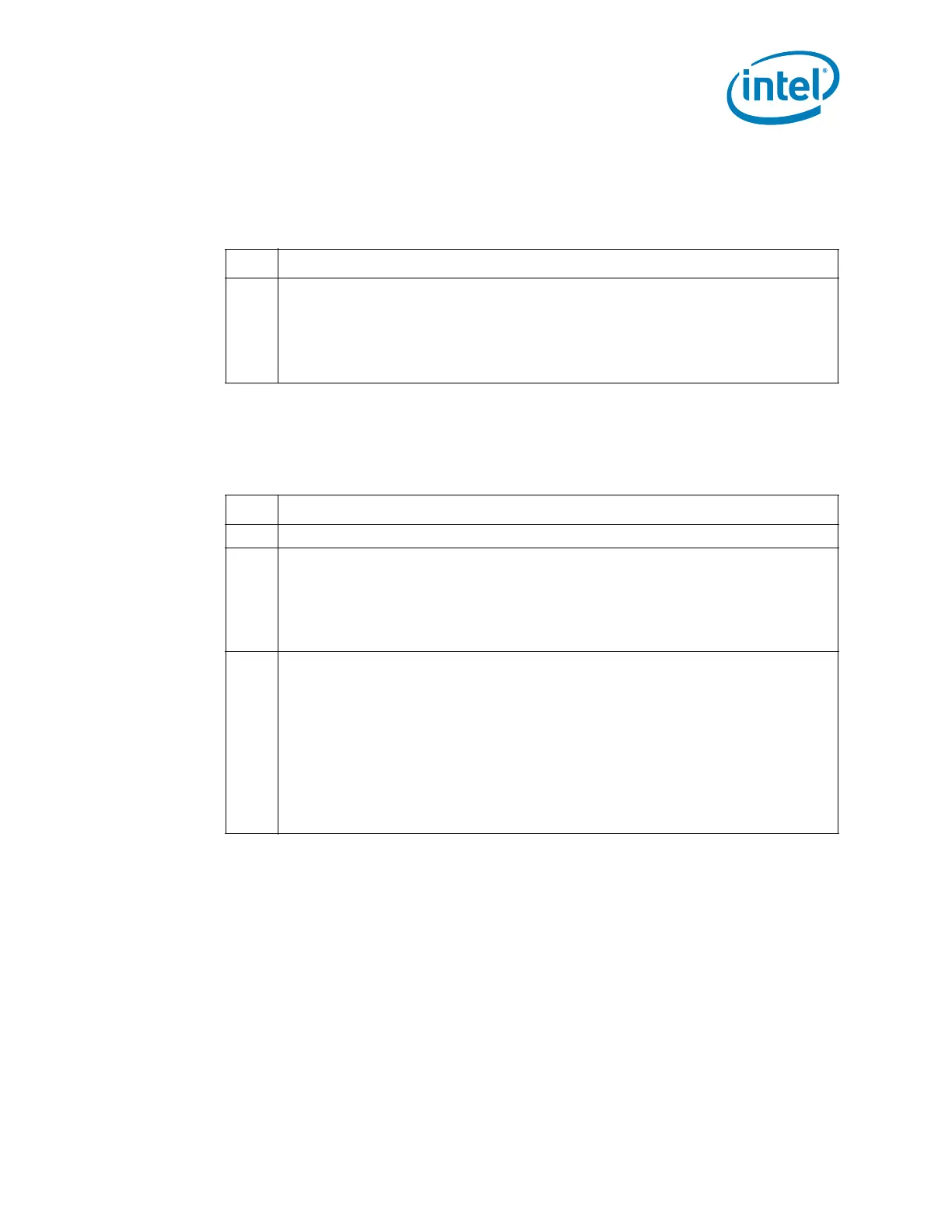

Memory Address:HDBAR + 64h Attribute: RO

Default Value: 00000000h Size: 32 bits

17.1.2.32 IRS—Immediate Command Status Register

(Intel

®

High Definition Audio Controller—D27:F0)

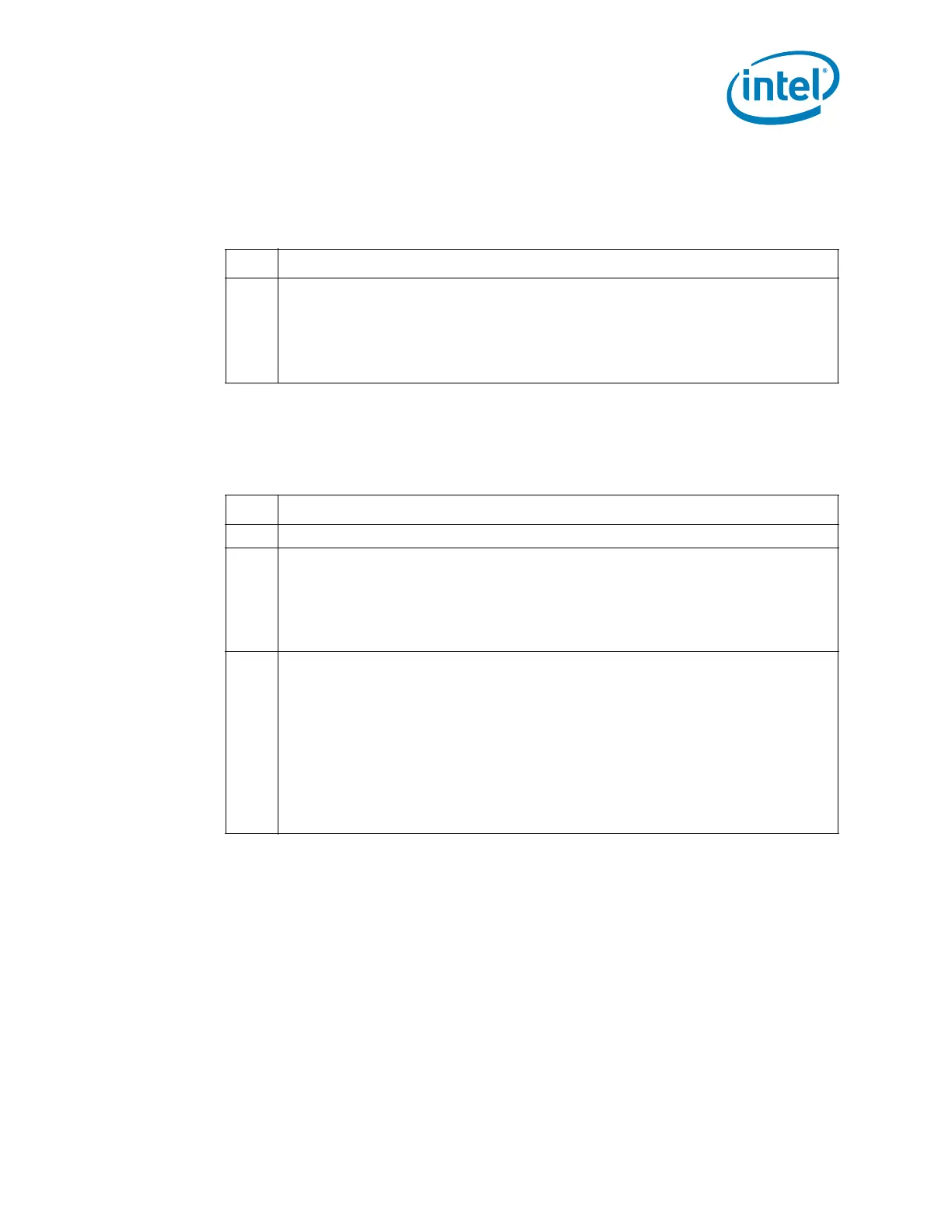

Memory Address:HDBAR + 68h Attribute: R/W, R/WC

Default Value: 0000h Size: 16 bits

Bit Description

31:0

Immediate Response Read (IRR) — RO. This register contains the response

received from a codec resulting from a command sent using the Immediate Command

mechanism.

If multiple codecs responded in the same time, there is no assurance as to which

response will be latched. Therefore, broadcast-type commands must not be issued

using the Immediate Command mechanism.

Bit Description

15:2 Reserved.

1

Immediate Result Valid (IRV) — R/WC.

1 = Set to 1 by hardware when a new response is latched into the Immediate Response

register (HDBAR + 64). This is a status flag indicating that software may read the

response from the Immediate Response register.

Software must clear this bit by writing a 1 to it before issuing a new command so that

the software may determine when a new response has arrived.

0

Immediate Command Busy (ICB) — R/W. When this bit is read as 0, it indicates that

a new command may be issued using the Immediate Command mechanism. When this

bit transitions from a 0 to a 1 (using software writing a 1), the controller issues the

command currently stored in the Immediate Command register to the codec over the

link. When the corresponding response is latched into the Immediate Response register,

the controller hardware sets the IRV flag and clears the ICB bit back to 0. Software may

write this bit to a 0 if the bit fails to return to 0 after a reasonable time out period.

NOTE: An Immediate Command must not be issued while the CORB/RIRB mechanism

is operating, otherwise the responses conflict. This must be enforced by

software.

Loading...

Loading...