Datasheet 731

Integrated Intel

®

High Definition Audio Controller Registers

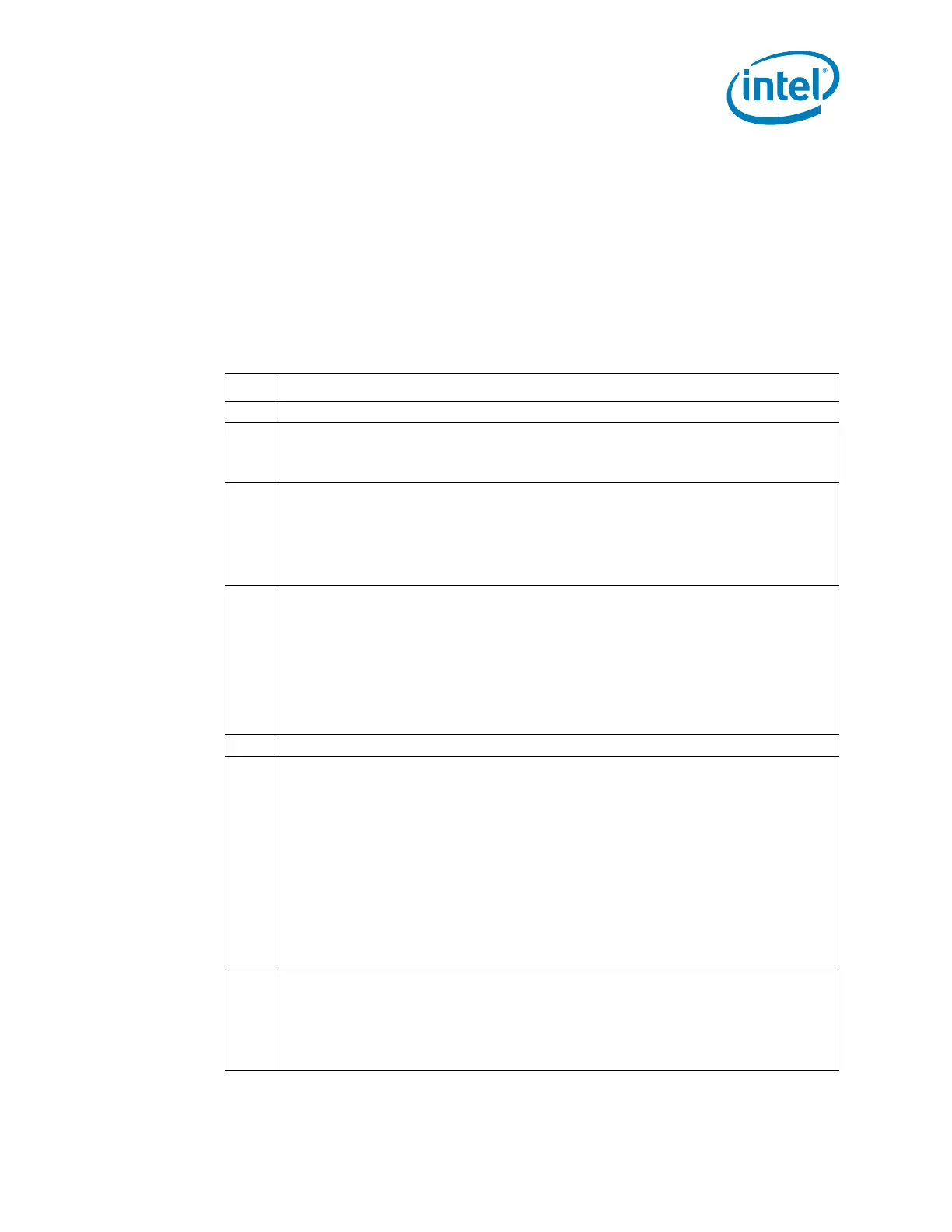

17.1.2.43 SDFMT—Stream Descriptor Format Register

(Intel

®

High Definition Audio Controller—D27:F0)

Memory Address:Input Stream[0]: HDBAR + 92h Attribute: R/W

Input Stream[1]: HDBAR + B2h

Input Stream[2]: HDBAR + D2h

Input Stream[3]: HDBAR + F2h

Output Stream[0]: HDBAR + 112h

Output Stream[1]: HDBAR + 132h

Output Stream[2]: HDBAR + 152h

Output Stream[3]: HDBAR + 172h

Default Value: 0000h Size: 16 bits

Bit Description

15 Reserved.

14

Sample Base Rate — R/W

0 = 48 kHz

1 = 44.1 kHz

13:11

Sample Base Rate Multiple — R/W

000 = 48 kHz, 44.1 kHz or less

001 = x2 (96 kHz, 88.2 kHz, 32 kHz)

010 = x3 (144 kHz)

011 = x4 (192 kHz, 176.4 kHz)

Others = Reserved.

10:8

Sample Base Rate Devisor — R/W.

000 = Divide by 1(48 kHz, 44.1 kHz)

001 = Divide by 2 (24 kHz, 22.05 kHz)

010 = Divide by 3 (16 kHz, 32 kHz)

011 = Divide by 4 (11.025 kHz)

100 = Divide by 5 (9.6 kHz)

101 = Divide by 6 (8 kHz)

110 = Divide by 7

111 = Divide by 8 (6 kHz)

7 Reserved.

6:4

Bits per Sample (BITS) — R/W.

000 =8 bits. The data will be packed in memory in 8-bit containers on 16-bit

boundaries

001 =16 bits. The data will be packed in memory in 16-bit containers on 16-bit

boundaries

010 = 20 bits. The data will be packed in memory in 32-bit containers on 32-bit

boundaries

011 =24 bits. The data will be packed in memory in 32-bit containers on 32-bit

boundaries

100 =32 bits. The data will be packed in memory in 32-bit containers on 32-bit

boundaries

Others = Reserved.

3:0

Number of Channels (CHAN) — R/W. Indicates number of channels in each frame of the

stream.

0000 =1

0001 =2

........

1111 =16

Loading...

Loading...