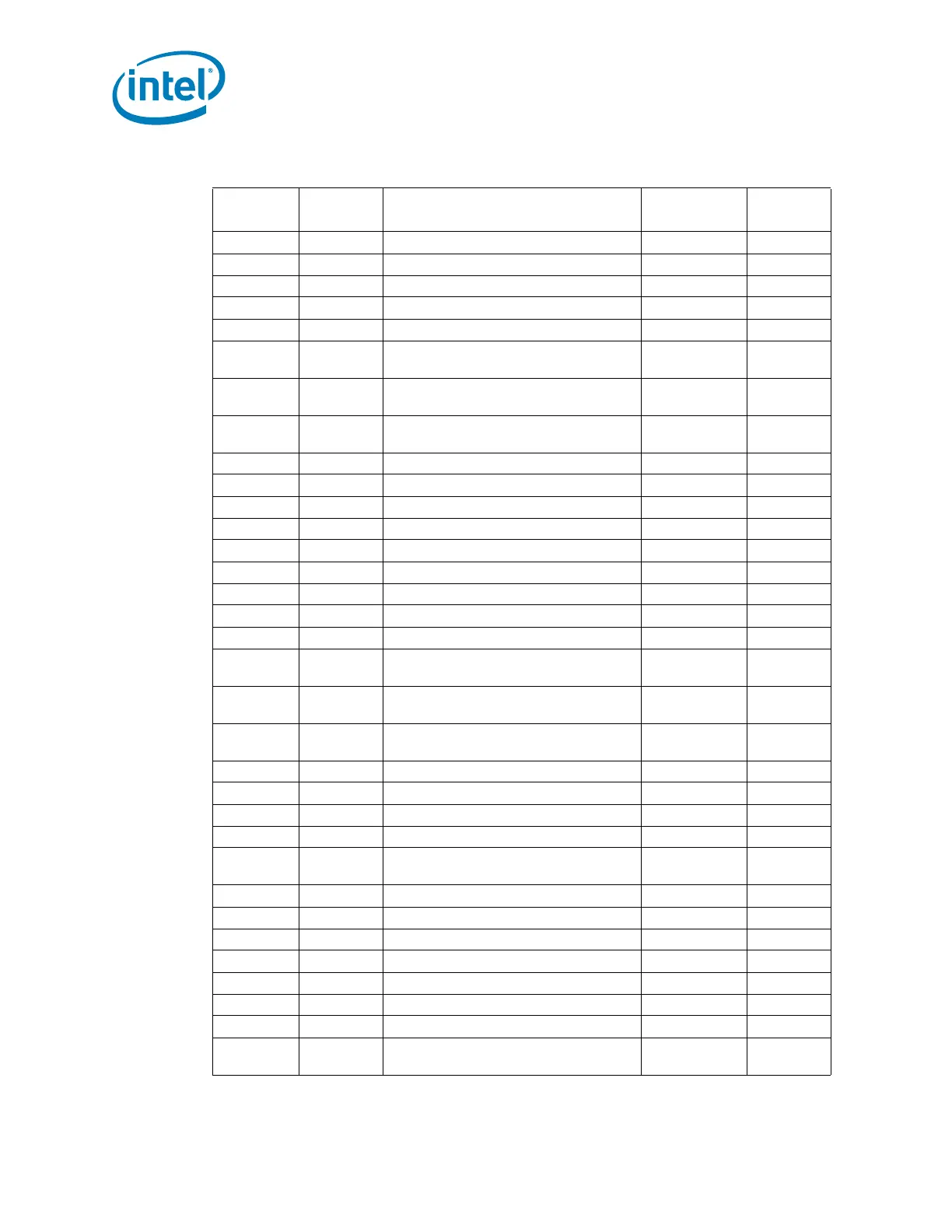

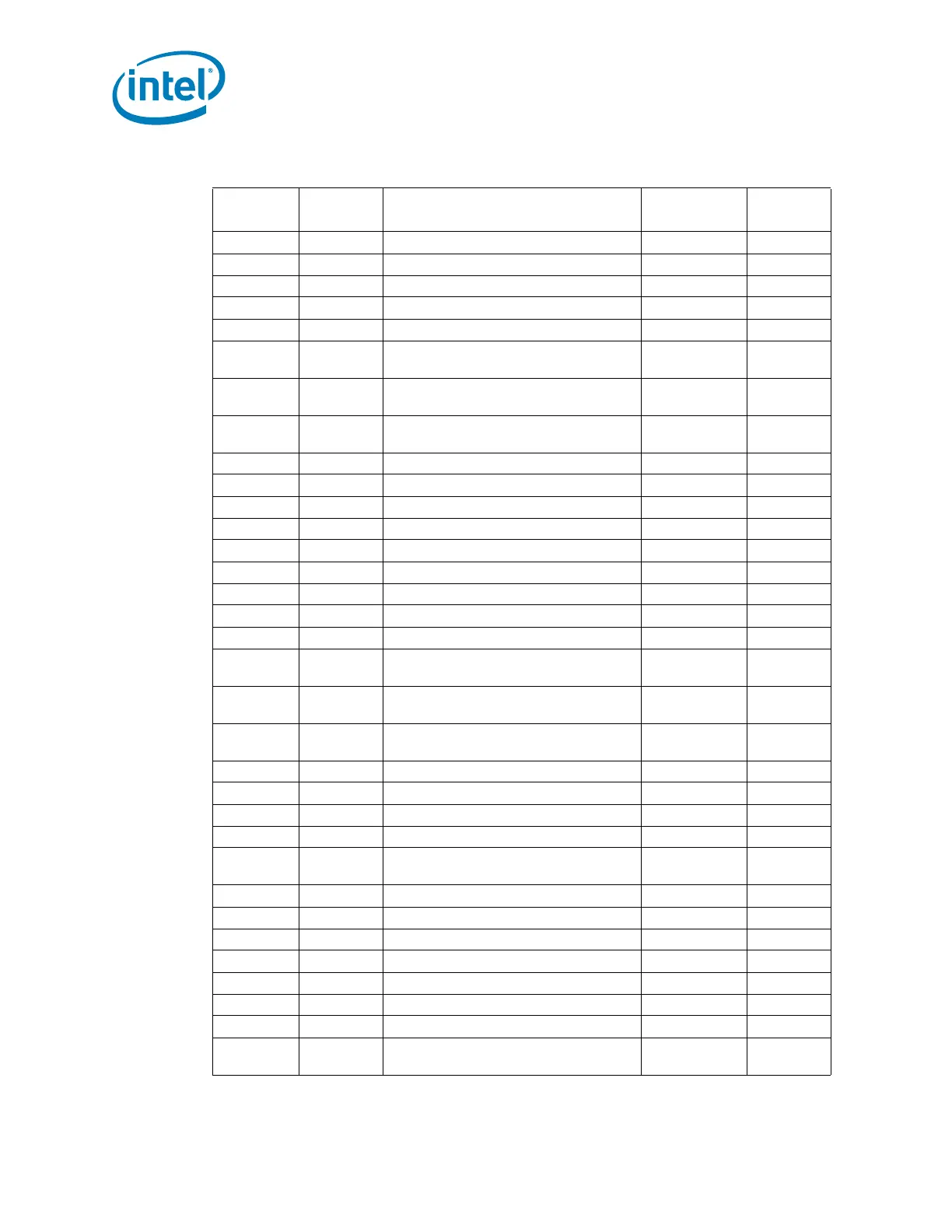

PCI Express* Configuration Registers

758 Datasheet

40h–41h CLIST Capabilities List 8010 RO

42h–43h XCAP PCI Express* Capabilities 0041 R/WO, RO

44h–47h DCAP Device Capabilities 00000FE0h RO

48h–49h DCTL Device Control 0000h R/W, RO

4Ah–4Bh DSTS Device Status 0010h R/WC, RO

4Ch–4Fh LCAP Link Capabilities

See bit

description

R/W, RO,

R/WO

50h–51h LCTL Link Control 0000h

R/W, WO,

RO

52h–53h LSTS Link Status

See bit

description

RO

54h–57h SLCAP Slot Capabilities Register 00000060h R/WO, RO

58h–59h SLCTL Slot Control 0000h R/W, RO

5Ah–5Bh SLSTS Slot Status 0000h R/WC, RO

5Ch–5Dh RCTL Root Control 0000h R/W

60h–63h RSTS Root Status 00000000h R/WC, RO

64h–67h DCAP2 Device Capabilities 2 Register 00000016h RO

68h–69h DCTL2 Device Control 2 Register 0000h R/W, RO

70h–71h LCTL2 Link Control 2 Register 0001h RO

80h–81h MID Message Signaled Interrupt Identifiers 9005h RO

82h–83h MC

Message Signaled Interrupt Message

Control

0000h R/W, RO

84h–87h MA

Message Signaled Interrupt Message

Address

00000000h R/W

88h–89h MD

Message Signaled Interrupt Message

Data

0000h R/W

90h–91h SVCAP Subsystem Vendor Capability A00Dh RO

94h–97h SVID Subsystem Vendor Identification 00000000h R/WO

A0h–A1h PMCAP Power Management Capability 0001h RO

A2h–A3h PMC PCI Power Management Capability C802h RO

A4h–A7h PMCS

PCI Power Management Control and

Status

00000000h R/W, RO

D4h–D7h MPC2 Miscellaneous Port Configuration 2 00000000h R/W, RO

D8h–DBh MPC Miscellaneous Port Configuration 08110000h R/W

DCh–DFh SMSCS SMI/SCI Status Register 00000000h R/WC

E1h RPDCGEN Rort Port Dynamic Clock Gating Enable 00h R/W

E8h–EBh PECR1 PCI Express Configuration Register 1 00000020h R/W

ECh–EFh PECR3 PCI Express Configuration Register 3 00000000h R/W, RO

11Ch–143h — Reserved — —

104h–107h UES Uncorrectable Error Status

See bit

description

R/WC, RO

Table 19-1. PCI Express* Configuration Registers Address Map

(PCI Express*—D28:F0/F1/F2/F3/F4/F5/F6/F7) (Sheet 2 of 3)

Offset Mnemonic Register Name

Function 0–5

Default

Type

Loading...

Loading...