Thermal Sensor Registers (D31:F6)

856 Datasheet

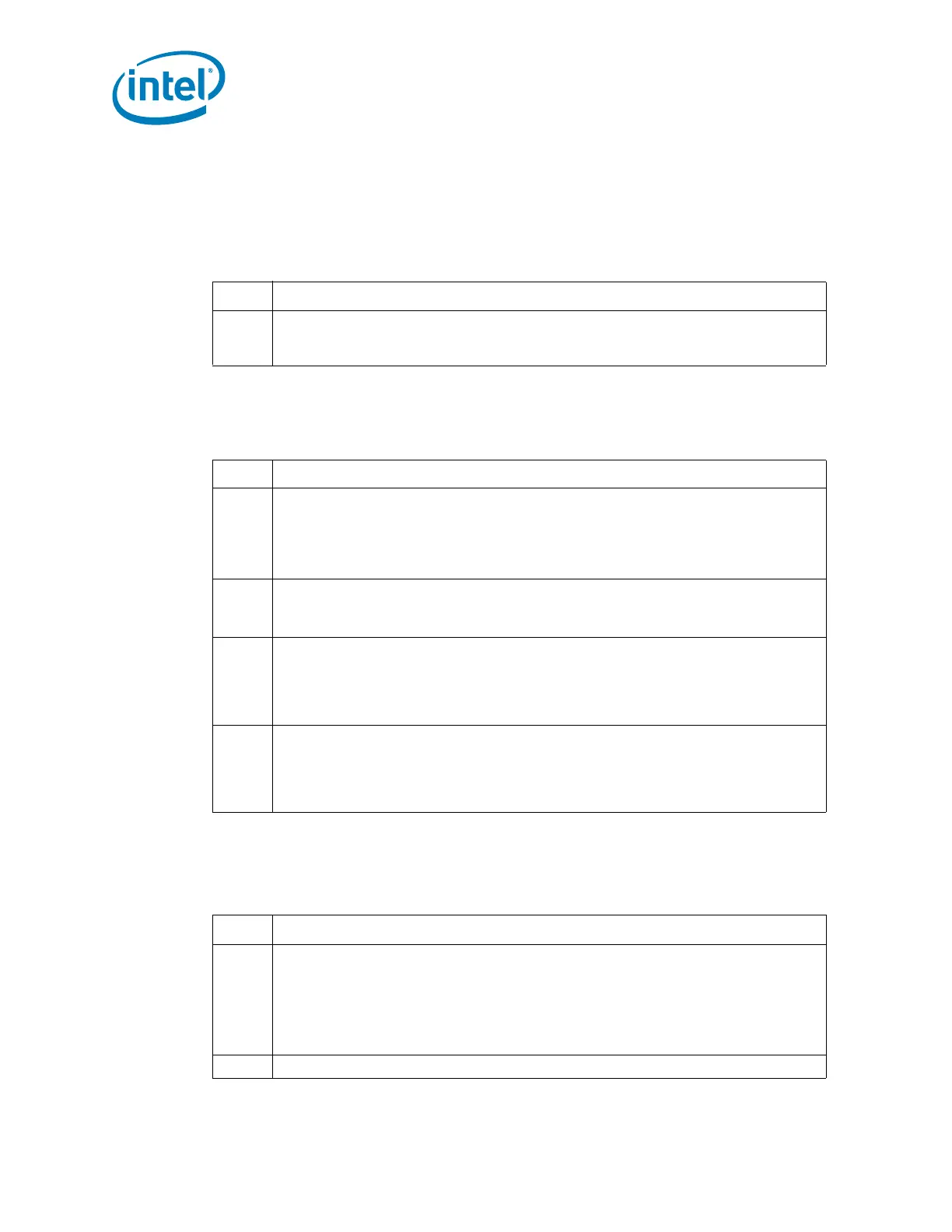

22.2.4 TSTR — Thermal Sensor Thermometer Read

Offset Address: TBARB+03h Attribute: RO

Default Value: FFh Size: 8 bit

This register generally provides the calibrated temperature from the thermometer

circuit when the thermometer is enabled.

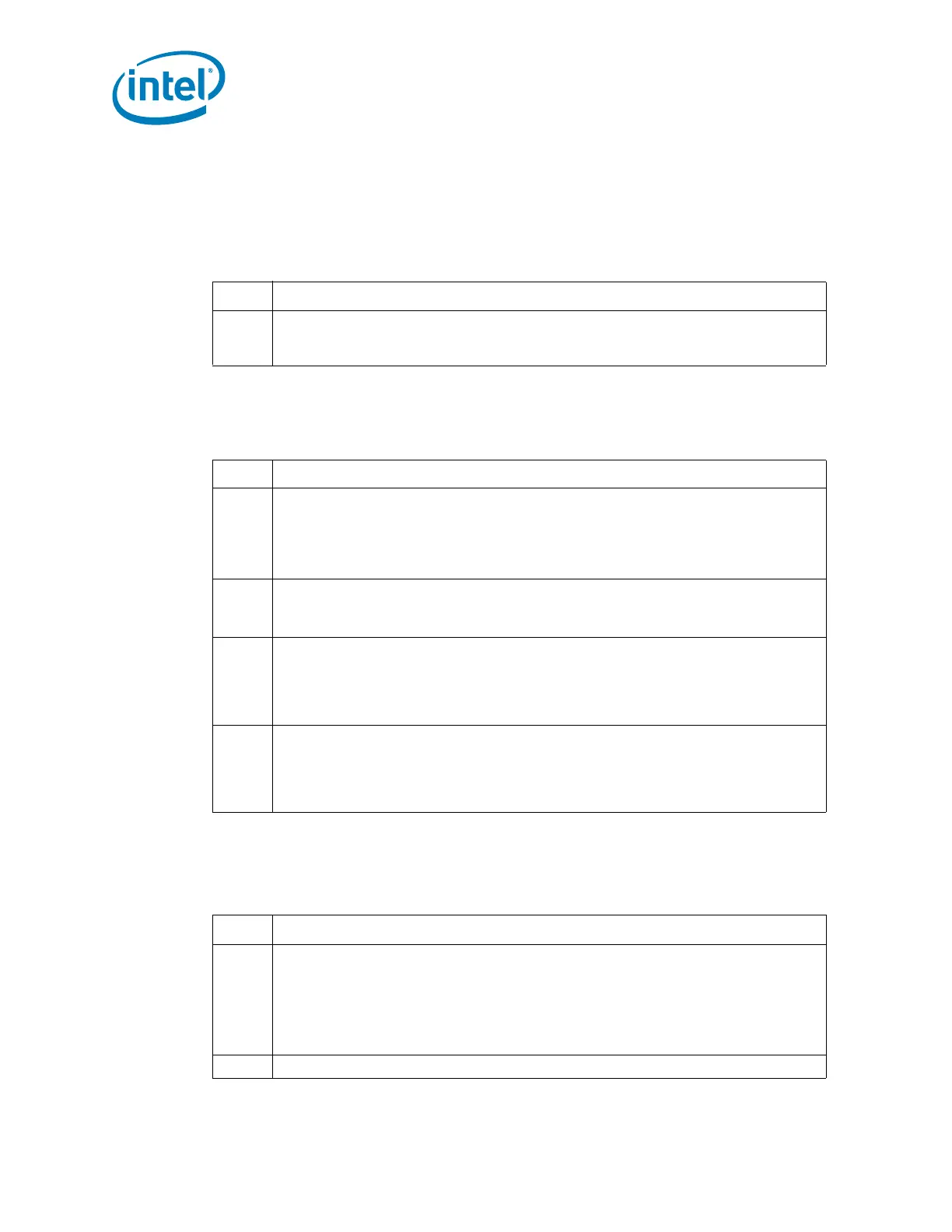

22.2.5 TSTTP—Thermal Sensor Temperature Trip Point

Offset Address: TBARB+04h Attribute: R/W

Default Value: 00000000h Size: 32 bit

22.2.6 TSCO—Thermal Sensor Catastrophic Lock-Down

Offset Address: TBARB+08h Attribute: R/W

Default Value: 00h Size: 8 bit

Bit Description

7:0

Thermometer Reading (TR)— RO. Value corresponds to the thermal sensor

temperature. This register has a straight binary encoding that ranges from 0 to FFh.

The value in this field is valid only if the TR value is between 00h and 7Fh.

Bit Description

31:24

Auxiliary2 Trip Point Setting (A2TPS) — R/W. These bits set the Auxiliary2 trip

point.

These bits are lockable using programming the policy-lock down bit (bit 7) of TSPC

register.

These bits may only be programmed from 0h to 7Fh. Setting bit 31 is illegal.

23:16

Auxiliary Trip Point Setting (ATPS) — R/W. These bits set the Auxiliary trip point.

These bits are lockable using TSLOCK bit 2

These bits may only be programmed from 0h to 7Fh. Setting bit 23 is illegal.

15:8

Hot Trip Point Setting (HTPS) — R/W. These bits set the Hot trip point.

These bits are lockable using programming the policy-lock down bit (bit 7) of TSPC

register.

These bits may only be programmed from 0h to 7Fh. Setting bit 15 is illegal.

NOTE: BIOS should program to 3Ah for setting Hot Trip Point to 108 °C.

7:0

Catastrophic Trip Point Setting (CTPS) — R/W. These bits set the catastrophic trip

point.

These bits are lockable using TSCO.bit 7.

These bits may only be programmed from 0h to 7Fh. Setting bit 7 is illegal.

NOTE: BIOS should program to 2Bh for setting Catastrophic Trip Point to 120 °C.

Bit Description

7

Lock bit for Catastrophic (LBC) — R/W.

0 = Catastrophic programming interface is unlocked

1 = Locks the Catastrophic programming interface including TSTTP.bits[7:0].

This bit may only be set to a 0 by a host partitioned reset (note that CF9 warm reset is

a host partitioned reset). Writing a 0 to this bit has no effect.

TSCO.[7] is unlocked by default and can be locked through BIOS.

6:0 Reserved

Loading...

Loading...