Thermal Sensor Registers (D31:F6)

862 Datasheet

22.2.15 TT — Thermal Throttling

Offset Address: TBARB+6Ch Attribute: R/W

Default Value: 00000000h Size: 32 bit

22.2.16 PHL — PCH Hot Level

Offset Address: TBARB+70h Attribute: R/W

Default Value: 00h Size: 8 bit

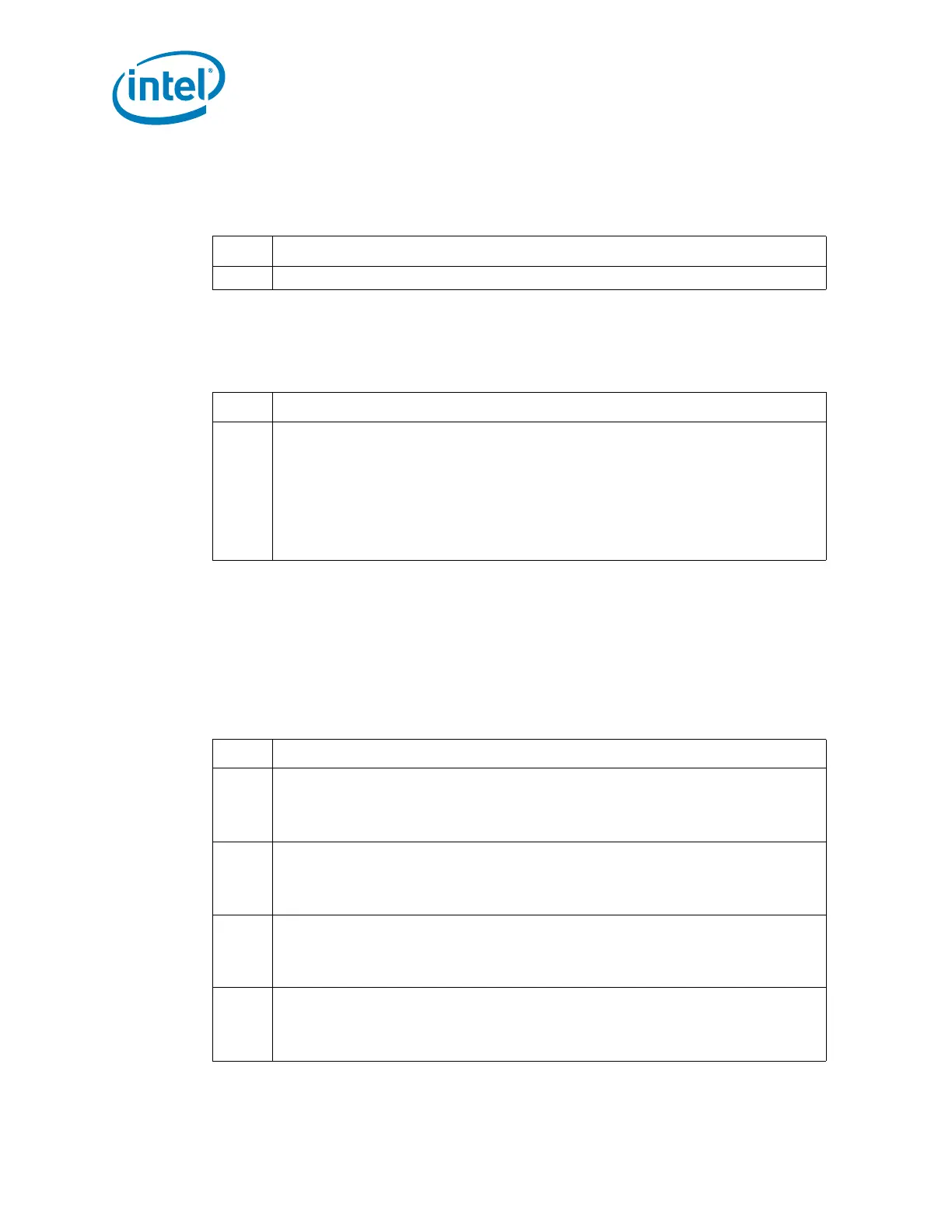

22.2.17 TSPIEN—Thermal Sensor PCI Interrupt Enable

Offset Address: TBARB+82h Attribute: R/W

Default Value: 00h Size: 8 bit

This register controls the conditions that result in PCI interrupts to be signalled from

Thermal Sensor trip events. Software (device driver) needs to ensure that it can

support PCI interrupts, even though BIOS may enable PCI interrupt capability through

this register.

Bit Description

31:0 BIOS must program this field to 05201B16h

Bit Description

7:0

PCH Hot Level (PHL)— R/W.

When temperature reading in Thermal Sensor Thermometer Read (TSTR) is less than

PHL programmed here, this will assert PCHHOT# (active low). (Note that TSTR reading

of 00h is the hottest temperature and 7Fh is the lowest temperature.)

Default state for this register is PHL disabled (00h). For utilizing the PCHHOT#

functionality, a soft strap has to be configured and BIOS programs this PHL value.

Please refer to the SPI Flash Programming Guide Application Note and Intel ME FW

collaterals for information on enabling PCHHOT#.

Bit Description

7

Auxiliary2 High-to-Low Enable — R/W.

0 = Corresponding status bit does not result in PCI interrupt.

1 = PCI interrupt is signaled when the corresponding status bit is set in the Thermal

Error Status Register.

6

Catastrophic High-to-Low Enable — R/W.

0 = Corresponding status bit does not result in PCI interrupt.

1 = PCI interrupt is signaled when the corresponding status bit is set in the Thermal

Error Status Register.

5

Hot High-to-Low Enable — R/W.

0 = Corresponding status bit does not result in PCI interrupt.

1 = PCI interrupt is signaled when the corresponding status bit is set in the Thermal

Error Status Register.

4

Auxiliary High-to-Low Enable — R/W.

0 = Corresponding status bit does not result in PCI interrupt.

1 = PCI interrupt is signaled when the corresponding status bit is set in the Thermal

Error Status Register.

Loading...

Loading...