Datasheet 863

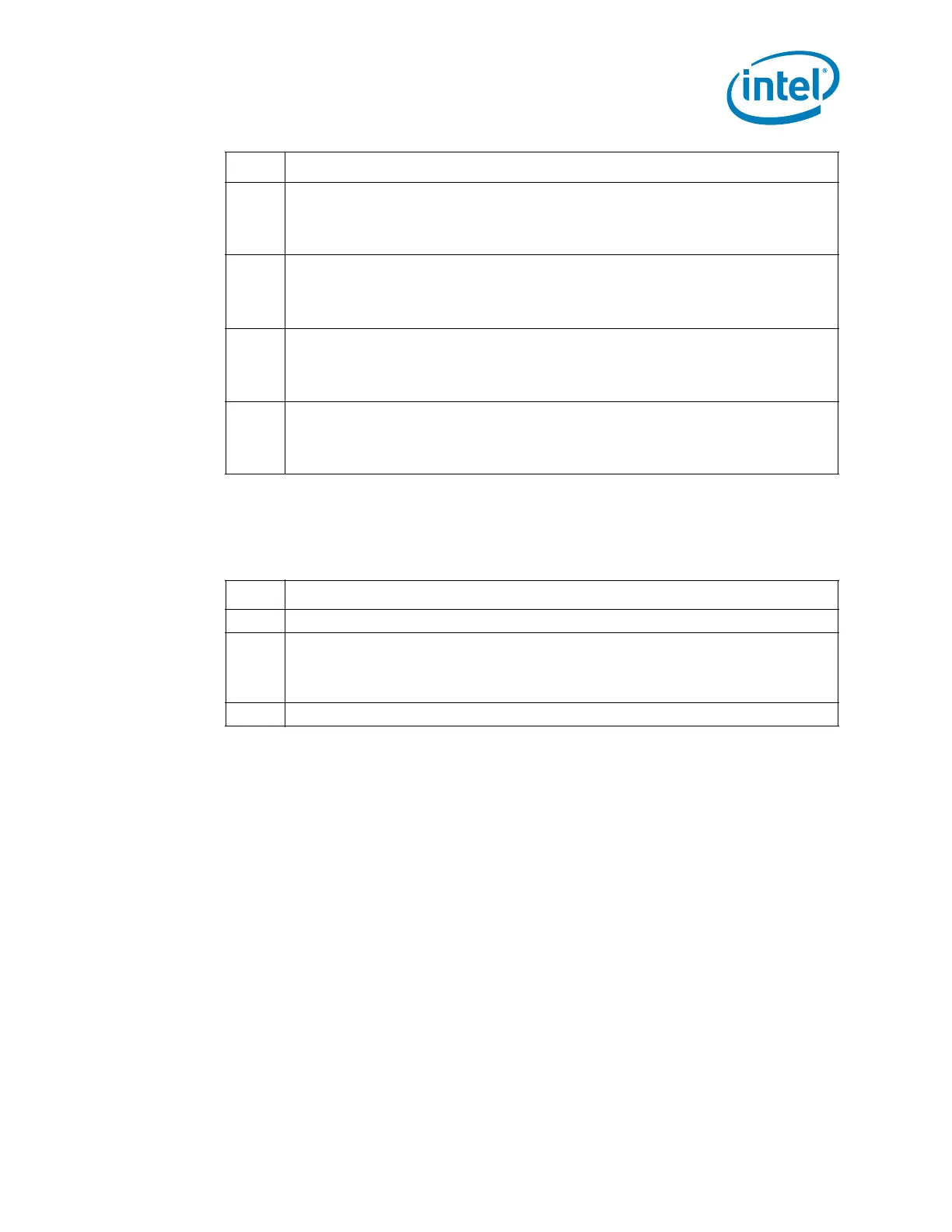

Thermal Sensor Registers (D31:F6)

22.2.18 TSLOCK—Thermal Sensor Register Lock Control

Offset Address: TBARB+83h Attribute: R/W

Default Value: 00h Size: 8 bit

3

Auxiliary2 Low-to-High Enable — R/W.

0 = Corresponding status bit does not result in PCI interrupt.

1 = PCI interrupt is signaled when the corresponding status bit is set in the Thermal

Error Status Register.

2

Catastrophic Low-to-High Enable — R/W.

0 = Corresponding status bit does not result in PCI interrupt.

1 = PCI interrupt is signaled when the corresponding status bit is set in the Thermal

Error Status Register.

1

Hot Low-to-High Enable— R/W.

0 = Corresponding status bit does not result in PCI interrupt.

1 = PCI interrupt is signaled when the corresponding status bit is set in the Thermal

Error Status Register.

0

Auxiliary Low-to-High Enable — R/W.

0 = Corresponding status bit does not result in PCI interrupt.

1 = PCI interrupt is signaled when the corresponding status bit is set in the Thermal

Error Status Register.

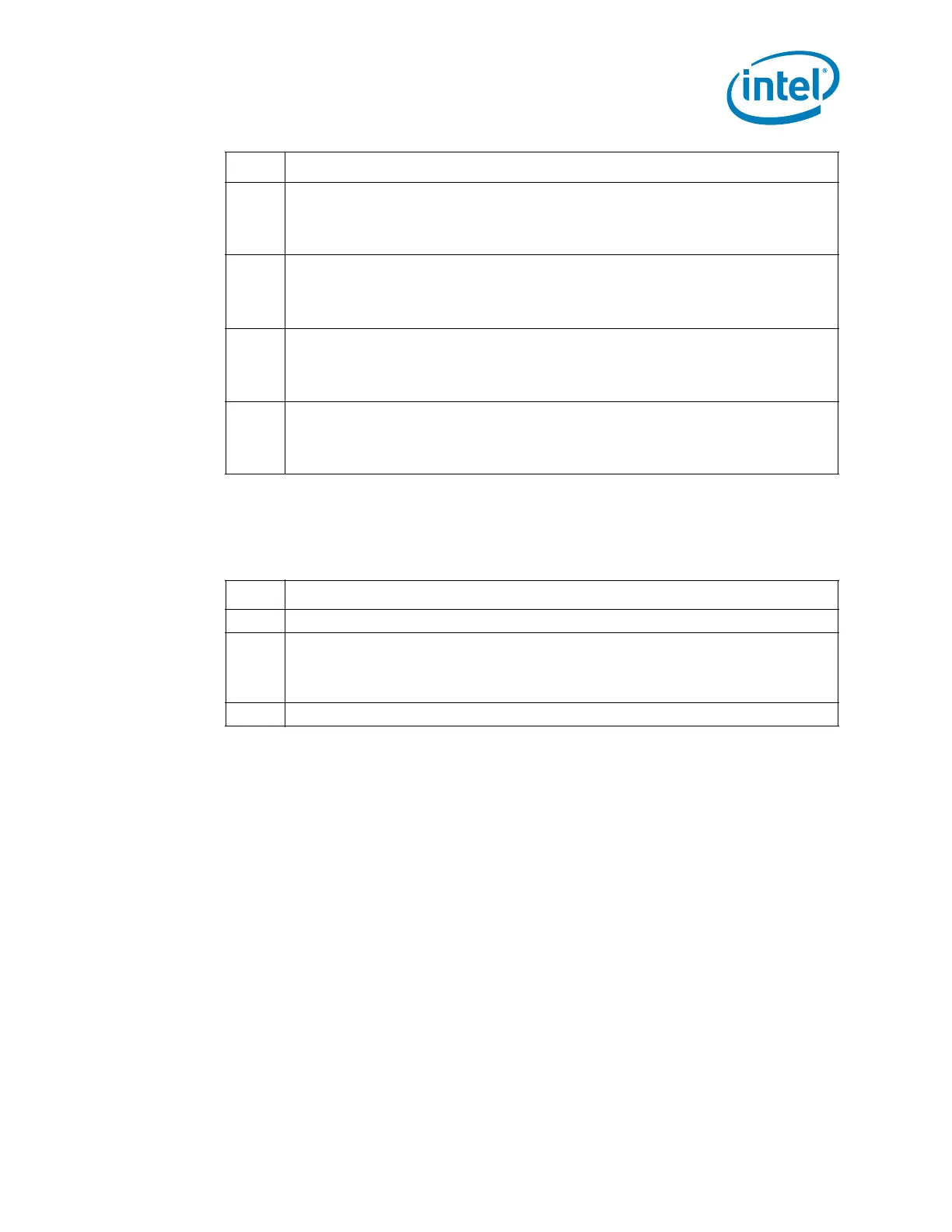

Bit Description

Bit Description

7:3 Reserved

2

Lock Control — R/W. This bit can only be set to a 0 by a host-partitioned reset.

Writing a 0 to this bit has no effect.

NOTE: CF9 warm reset is a host-partitioned reset.

1:0 Reserved

Loading...

Loading...