Rev. 1.50, 10/04, page 105 of 448

6.3.2 Floating-Point Status/Control Register (FPSCR)

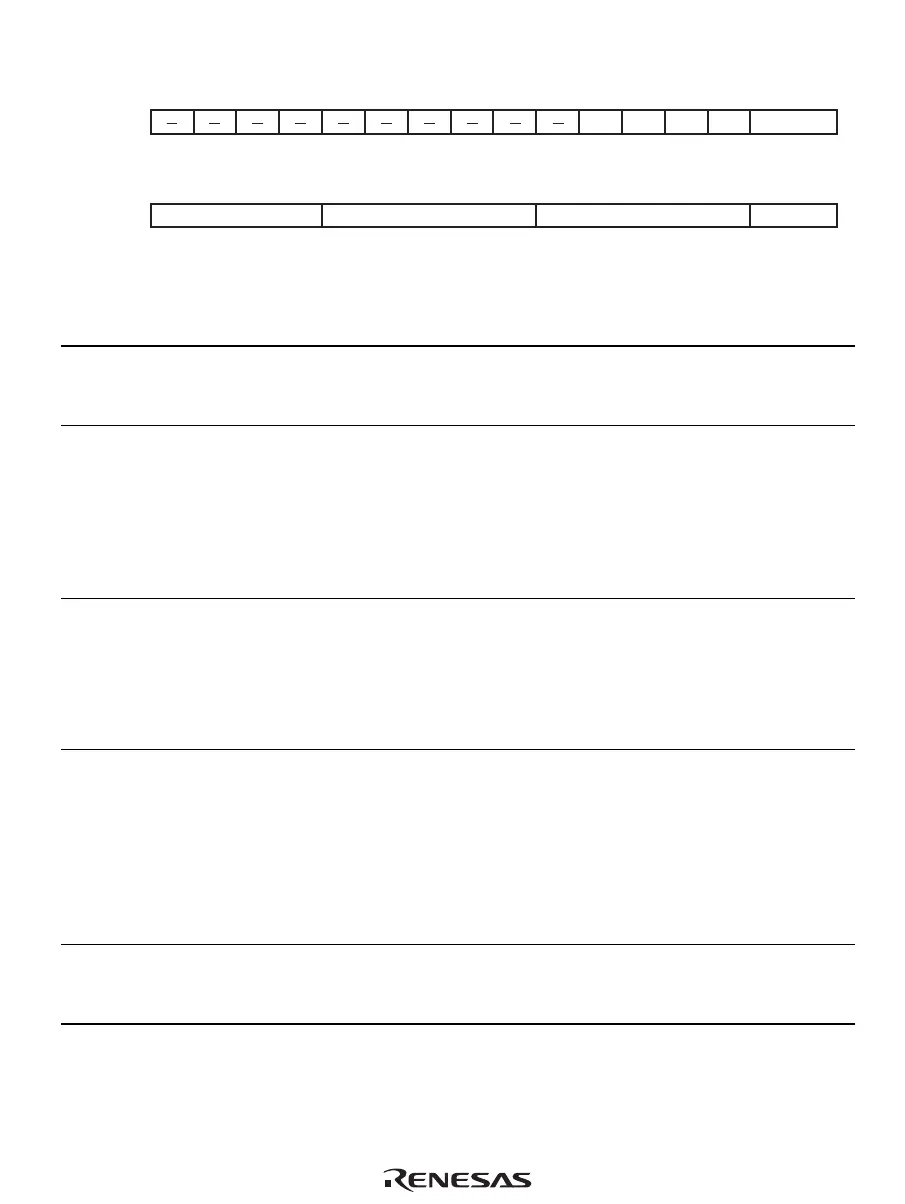

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

bit:

0000000000000100

Initial value:

RRRRRRRRRRR/WR/WR/WR/WR/WR/W

R/W:

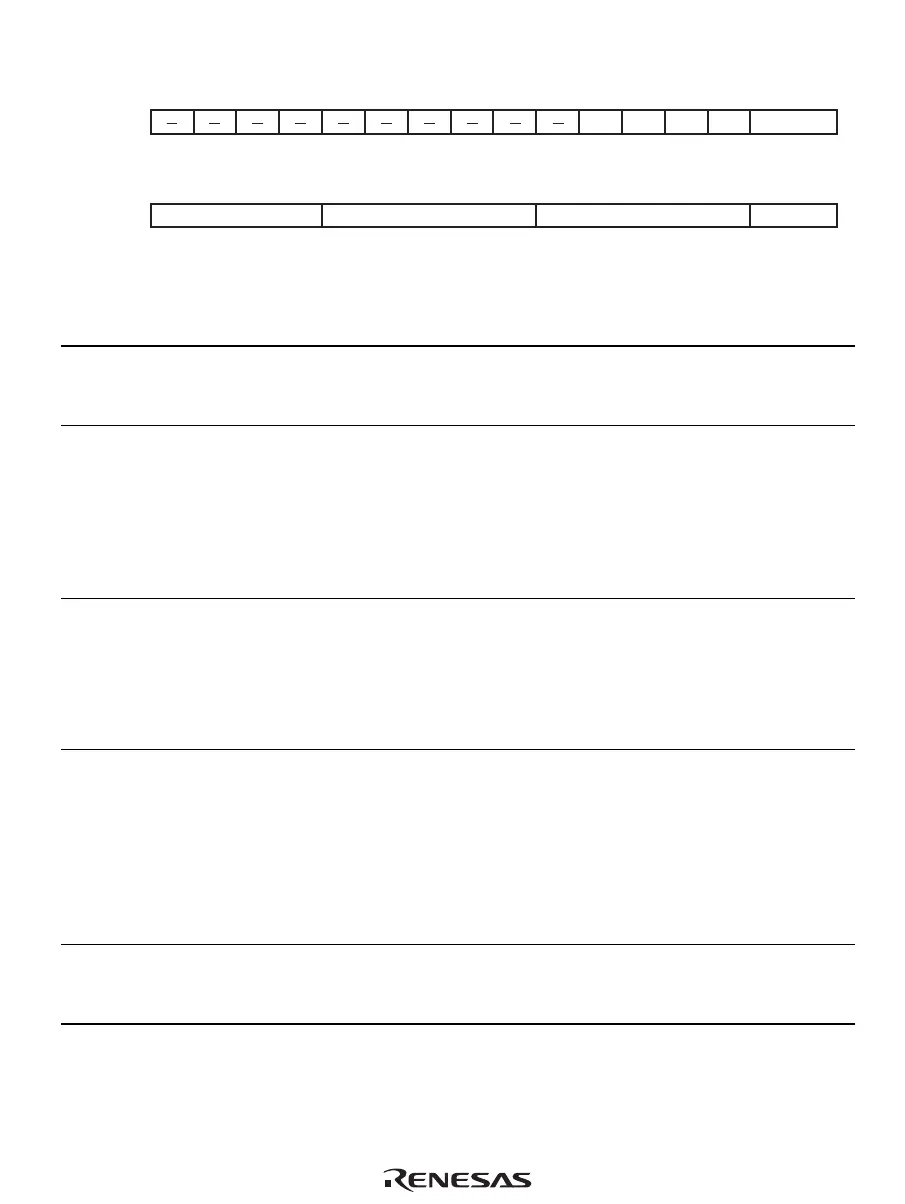

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1

0

bit:

0000000000000001

Initial value:

R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W

R/W:

Enable (EN)

FR SZ PR DN

Flag RM

Cause

Cause

Bit Bit Name

Initial

Value R/W Description

31 to 22 — All 0 R Reserved

These bits are always read as 0. The write value should

always be 0.

21 FR 0 R/W Floating-Point Register Bank

0: FPR0_BANK0 to FPR15_BANK0 are assigned to

FR0 to FR15 and FPR0_BANK1 to FPR15_BANK1

are assigned to XF0 to XF15

1: FPR0_BANK0 to FPR15_BANK0 are assigned to

XF0 to XF15 and FPR0_BANK1 to FPR15_BANK1

are assigned to FR0 to FR15

20 SZ 0 R/W Transfer Size Mode

0: Data size of FMOV instruction is 32-bits

1: Data size of FMOV instruction is a 32-bit register

pair (64 bits)

For relations between endian and the SZ and PR bits,

see figure 6.5.

19 PR 0 R/W Precision Mode

0: Floating-point instructions are executed as

single-precision operations

1: Floating-point instructions are executed as

double-precision operations (graphics support

instructions are undefined)

For relations between endian and the SZ and PR bits,

see figure 6.5.

18 DN 1 R/W Denormalization Mode

0: Denormalized number is treated as such

1: Denormalized number is treated as zero

Loading...

Loading...