Rev. 1.50, 10/04, page 125 of 448

7.2.5 MMU Control Register (MMUCR)

The individual bits perform MMU settings as shown below. Therefore, MMUCR rewriting should

be performed by a program in the P1 or P2 area.

After MMUCR has been updated, execute one of the following three methods before an access

(including an instruction fetch) to the P0, P3, U0, or store queue area is performed.

1. Execute a branch using the RTE instruction. In this case, the branch destination may be the P0,

P3, or U0 area.

2. Execute the ICBI instruction for any address (including non-cacheable area).

3. If the R2 bit in IRMCR is 0 (initial value) before updating MMUCR, the specific instruction

does not need to be executed. However, note that the CPU processing performance will be

lowered because the instruction fetch is performed again for the next instruction after

MMUCR has been updated.

Note that the method 3 may not be guaranteed in the future SuperH Series. Therefore, it is

recommended that the method 1 or 2 should be used for being compatible with the future SuperH

Series.

MMUCR contents can be changed by software. However, the LRUI and URC bits may also be

updated by hardware.

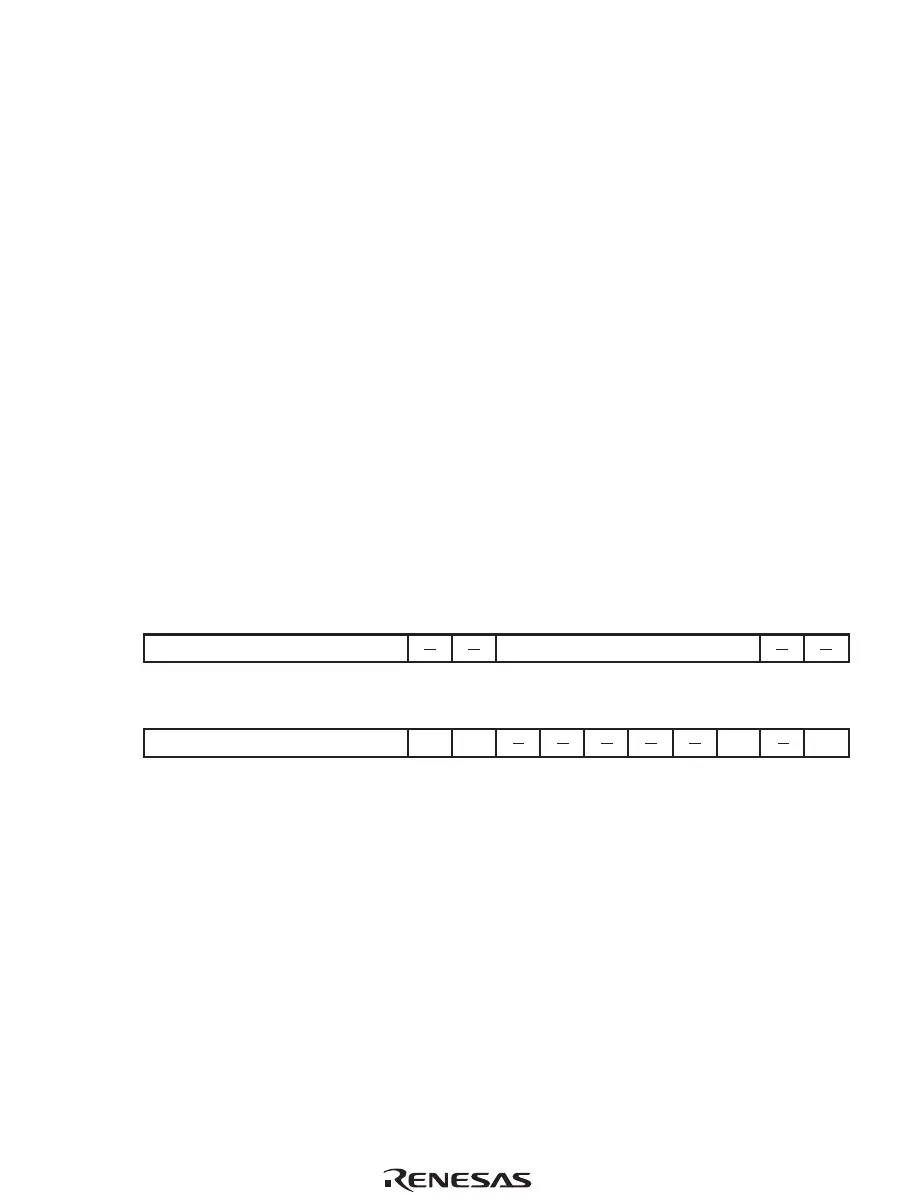

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Bit:

0000000000000000

Initial value:

R/W R/W R/W R/W R/W R/W R R R/W R/W R/W R/W R/W R/W R R

RRR

TI

URBLRUI

URC SQMD SV

AT

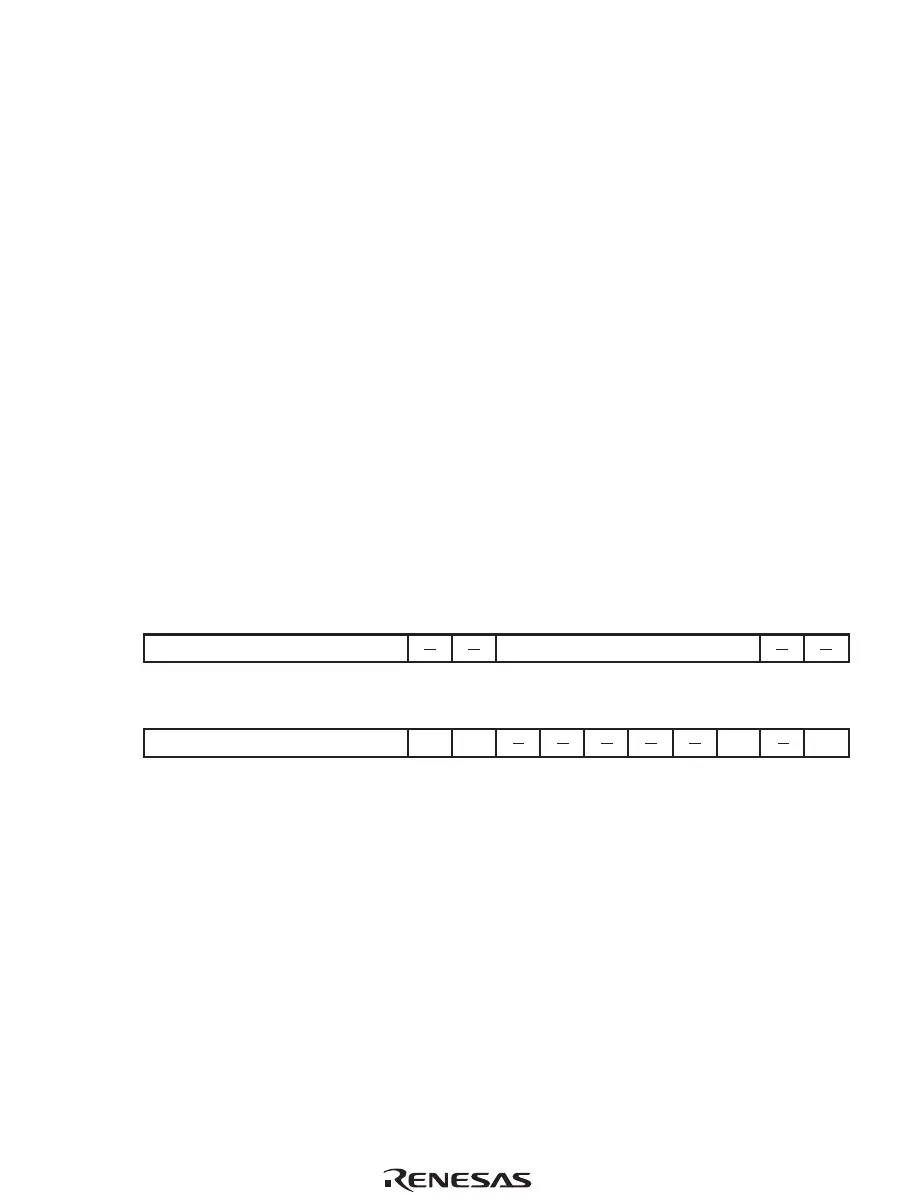

R R R/W R R/W

R/W:

Bit:

Initial value:

R/W:

1514131211109876543210

0000000000000 000

R/W R/W R/W R/W R/W R/W R/W

R/W

Loading...

Loading...