Rev. 1.50, 10/04, page 36 of 448

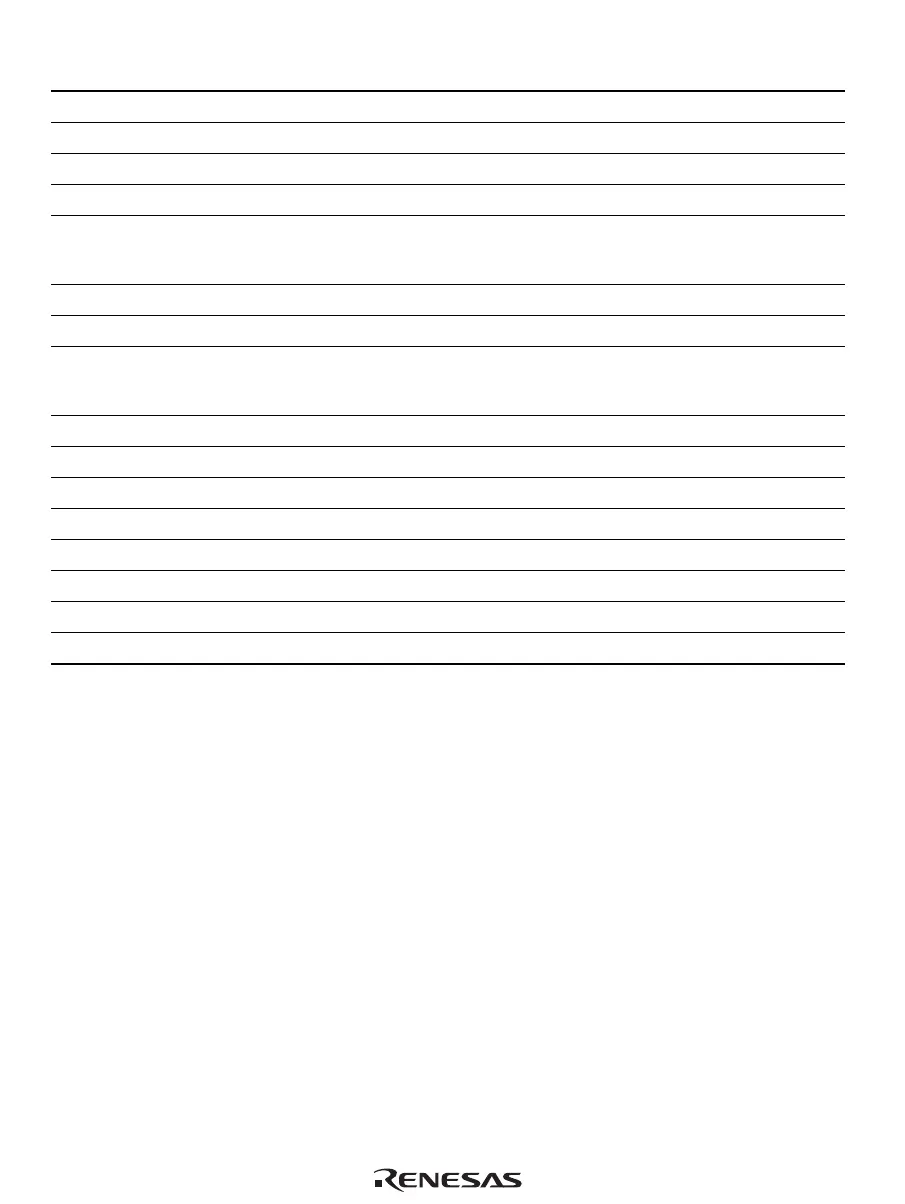

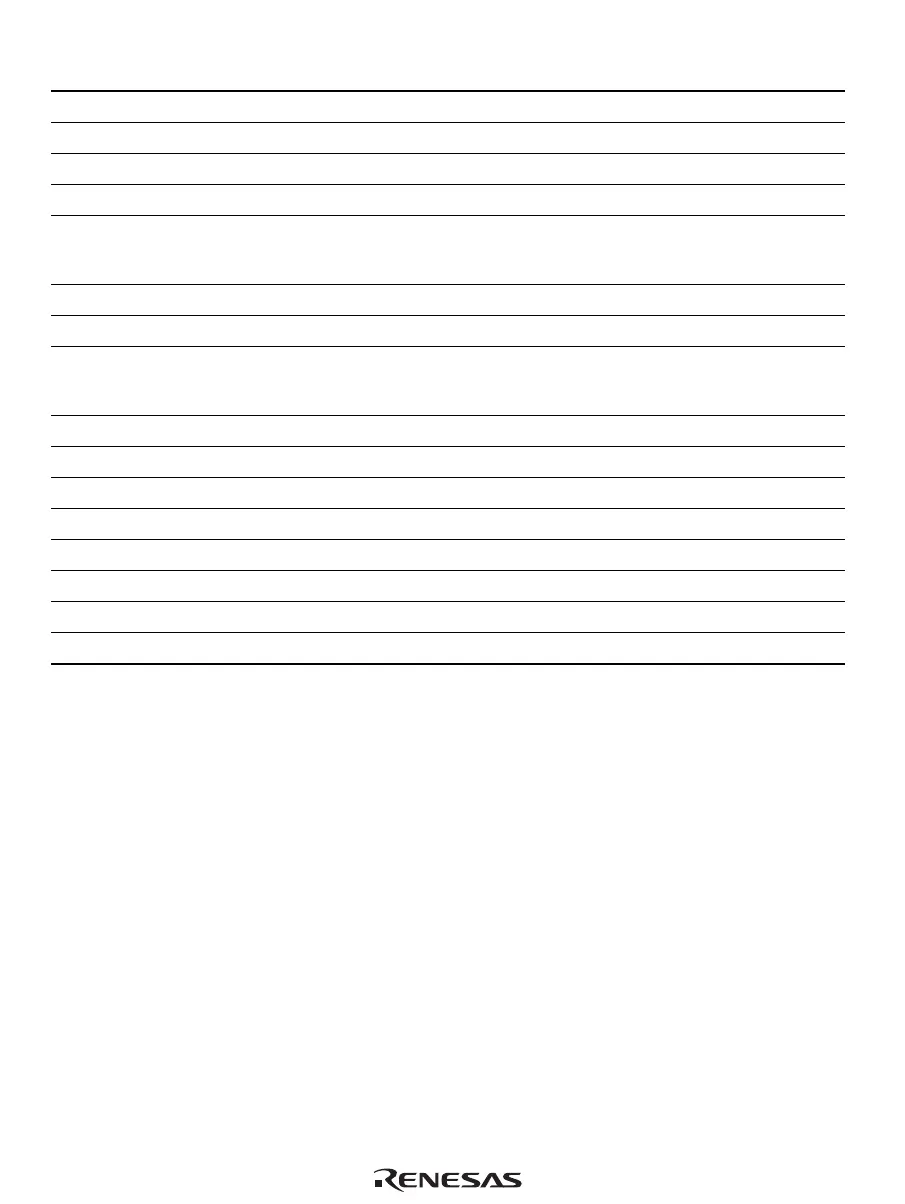

Table 3.7 Shift Instructions

Instruction Operation Instruction Code Privileged T Bit New

ROTL Rn T ← Rn ← MSB

0100nnnn00000100

— MSB —

ROTR Rn LSB → Rn → T

0100nnnn00000101

— LSB —

ROTCL Rn T ← Rn ← T

0100nnnn00100100

— MSB —

ROTCR Rn T → Rn → T

0100nnnn00100101

— LSB —

SHAD Rm,Rn When Rm ≥ 0, Rn << Rm → Rn

When Rm < 0, Rn >> Rm →

[MSB → Rn]

0100nnnnmmmm1100

— — —

SHAL Rn T ← Rn ← 0

0100nnnn00100000

— MSB —

SHAR Rn MSB → Rn → T

0100nnnn00100001

— LSB —

SHLD Rm,Rn When Rm ≥ 0, Rn << Rm → Rn

When Rm < 0, Rn >> Rm →

[0 → Rn]

0100nnnnmmmm1101

— — —

SHLL Rn T ← Rn ← 0

0100nnnn00000000

— MSB —

SHLR Rn 0 → Rn → T

0100nnnn00000001

— LSB —

SHLL2 Rn Rn << 2 → Rn

0100nnnn00001000

— — —

SHLR2 Rn Rn >> 2 → Rn

0100nnnn00001001

— — —

SHLL8 Rn Rn << 8 → Rn

0100nnnn00011000

— — —

SHLR8 Rn Rn >> 8 → Rn

0100nnnn00011001

— — —

SHLL16 Rn Rn << 16 → Rn

0100nnnn00101000

— — —

SHLR16 Rn Rn >> 16 → Rn

0100nnnn00101001

— — —

Loading...

Loading...