Rev. 1.50, 10/04, page 25 of 448

3.2 Addressing Modes

Addressing modes and effective address calculation methods are shown in table 3.2. When a

location in virtual memory space is accessed (AT in MMUCR = 1), the effective address is

translated into a physical memory address. If multiple virtual memory space systems are selected

(SV in MMUCR = 0), the least significant bit of PTEH is also referenced as the access ASID. For

details, see section 7, Memory Management Unit (MMU).

Table 3.2 Addressing Modes and Effective Addresses

Addressing

Mode

Instruction

Format Effective Address Calculation Method

Calculation

Formula

Register

direct

Rn Effective address is register Rn.

(Operand is register Rn contents.)

—

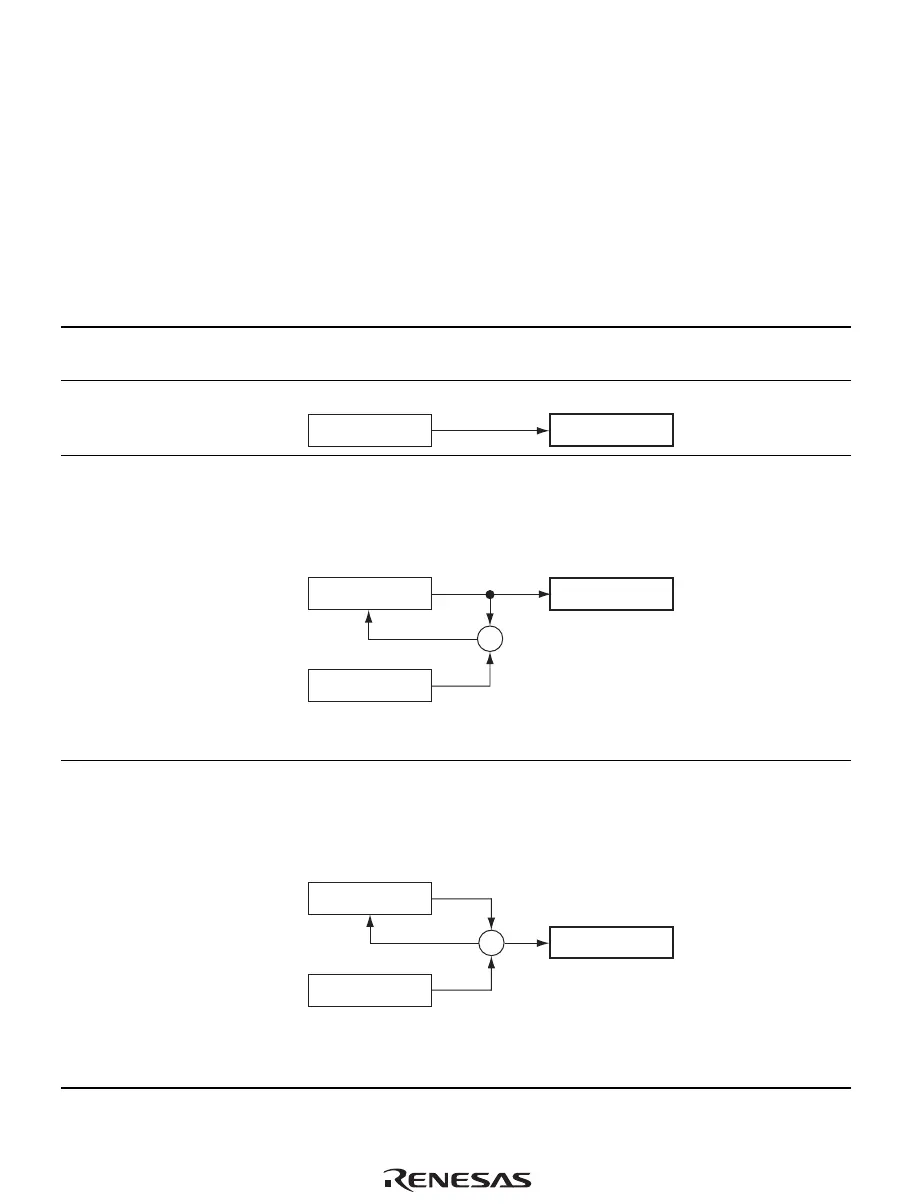

Register

indirect

@Rn Effective address is register Rn contents.

Rn Rn

Rn → EA

(EA: effective

address)

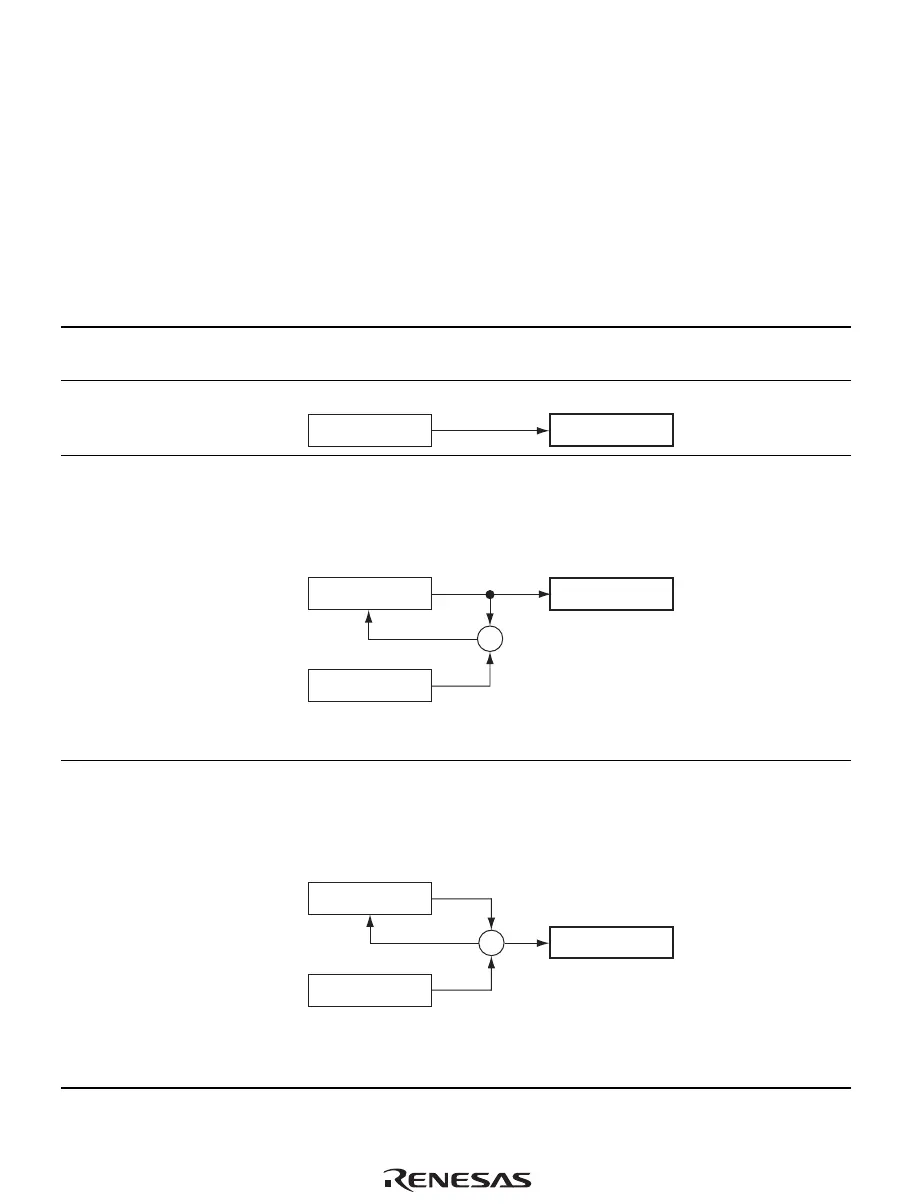

Register

indirect

with post-

increment

@Rn+ Effective address is register Rn contents.

A constant is added to Rn after instruction

execution: 1 for a byte operand, 2 for a word

operand, 4 for a longword operand, 8 for a

quadword operand.

Rn Rn

1/2/4

+

Rn + 1/2/4

Rn → EA

After

instruction

execution

Byte:

Rn + 1 → Rn

Word:

Rn + 2 → Rn

Longword:

Rn + 4 → Rn

Quadword:

Rn + 8 → Rn

Register

indirect

with pre-

decrement

@–Rn Effective address is register Rn contents,

decremented by a constant beforehand:

1 for a byte operand, 2 for a word operand,

4 for a longword operand, 8 for a quadword

operand.

Rn

1/2/4

Rn – 1/2/4/8

–

Rn – 1/2/4

Byte:

Rn – 1 → Rn

Word:

Rn – 2 → Rn

Longword:

Rn – 4 → Rn

Quadword:

Rn – 8 → Rn

Rn → EA

(Instruction

executed

with Rn after

calculation)

Loading...

Loading...