Rev. 1.50, 10/04, page 66 of 448

5.2.1 TRAPA Exception Register (TRA)

The TRAPA exception register (TRA) consists of 8-bit immediate data (imm) for the TRAPA

instruction. TRA is set automatically by hardware when a TRAPA instruction is executed. TRA

can also be modified by software.

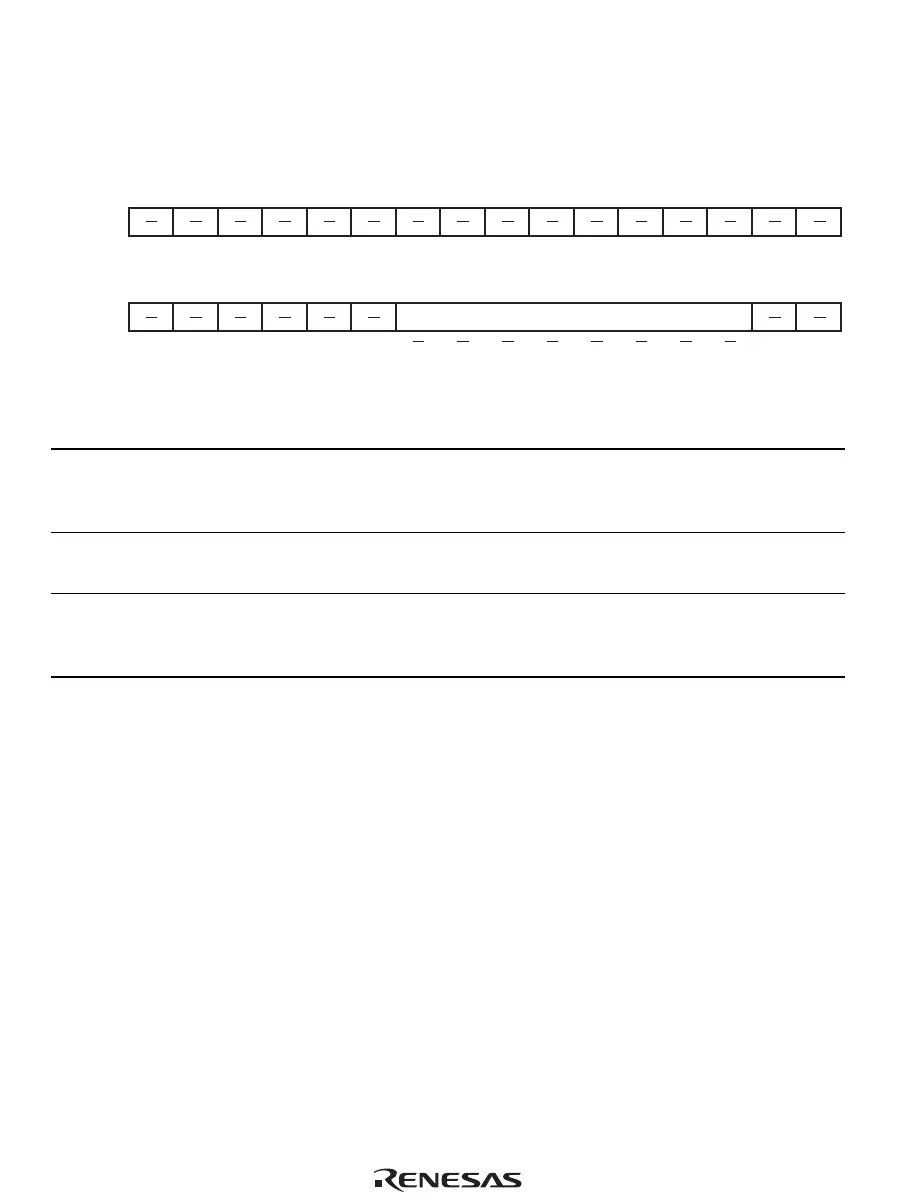

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Bit:

0000000000000000

00

Initial value:

RRRRRRRRRRRRRRRR

R/W R/W R/W

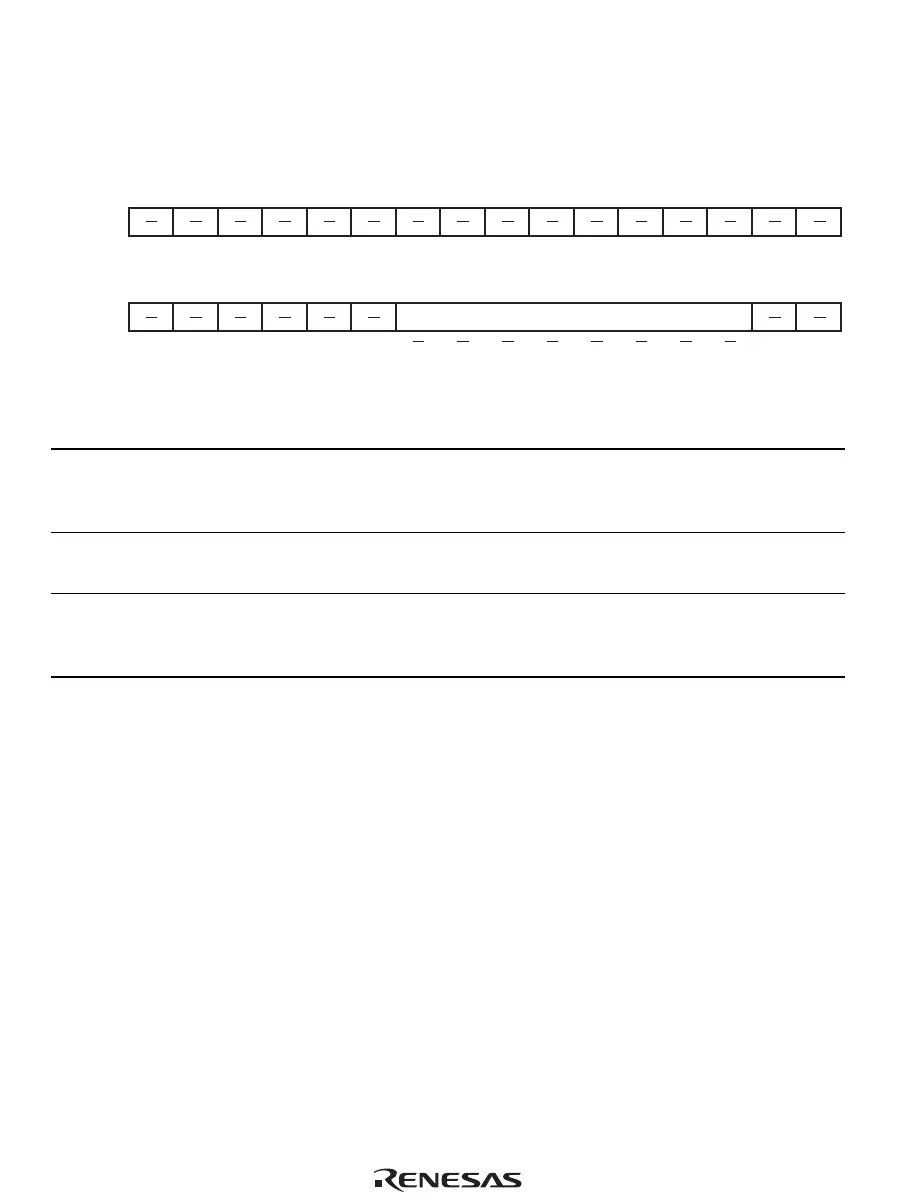

TRACODE

R/W R/W R/W R R

R/W:

Bit:

Initial value:

R/W:

1514131211109876543210

000000

RRRRRRR/W

R/W

Bit Bit Name

Initial

Value R/W Description

31 to 10 All 0 R Reserved

For details on reading/writing this bit, see General

Precautions on Handling of Product.

9 to 2 TRACODE Undefine

d

R/W TRAPA Code

8-bit immediate data of TRAPA instruction is set

1, 0 All 0 R Reserved

For details on reading/writing this bit, see General

Precautions on Handling of Product.

Loading...

Loading...