Rev. 1.50, 10/04, page 155 of 448

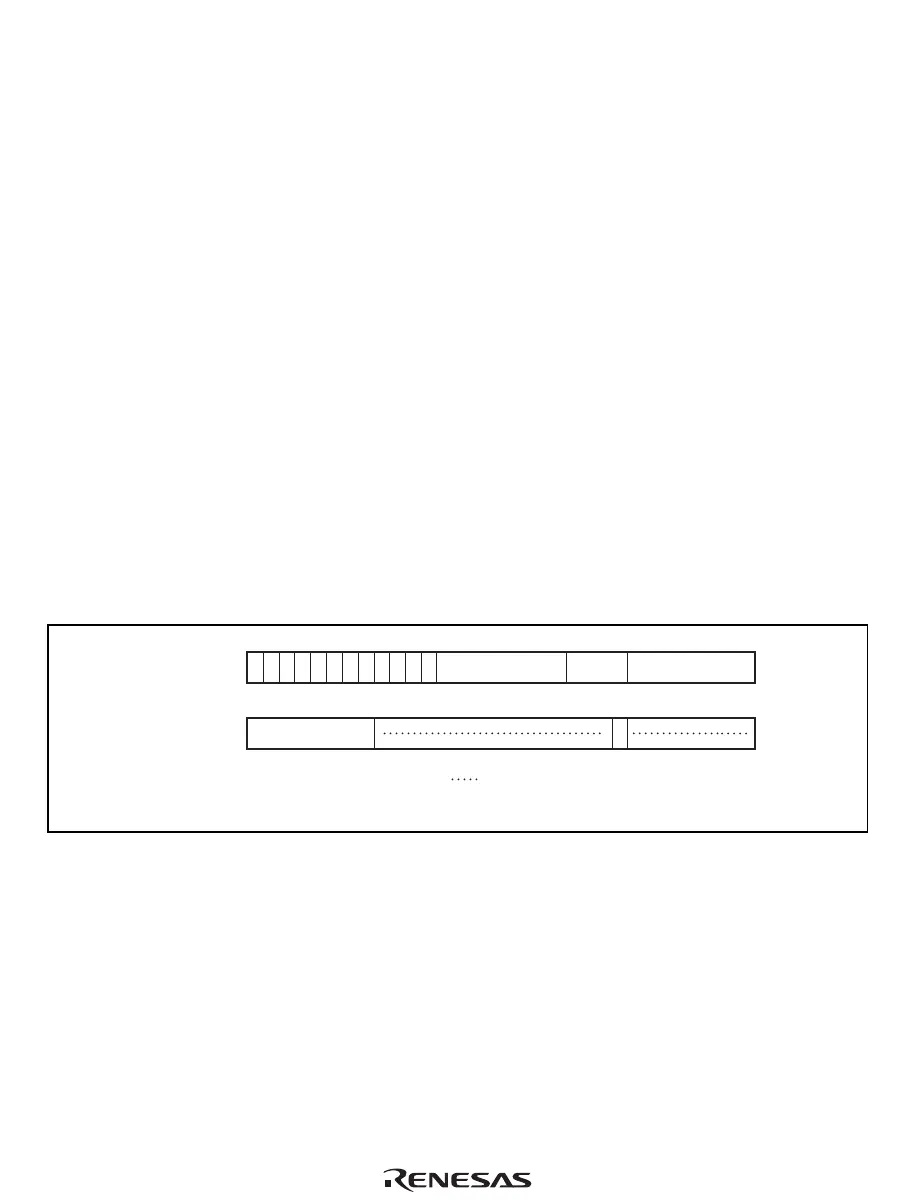

1. PMB address array read

When memory reading is performed while bits 31 to 20 in the address field are specified as

H'F61 which indicates the PMB address array and bits 11 to 8 in the address field as an entry,

bits 31 to 24 in the data field are read as VPN and bit 8 in the data field as V.

2. PMB address array write

When memory writing is performed while bits 31 to 20 in the address field are specified as

H'F61 which indicates the PMB address array and bits 11 to 8 in the address field as an entry,

and bits 31 to 24 in the data field are specified as VPN and bit 8 in the data field as V, data is

written to the specified entry.

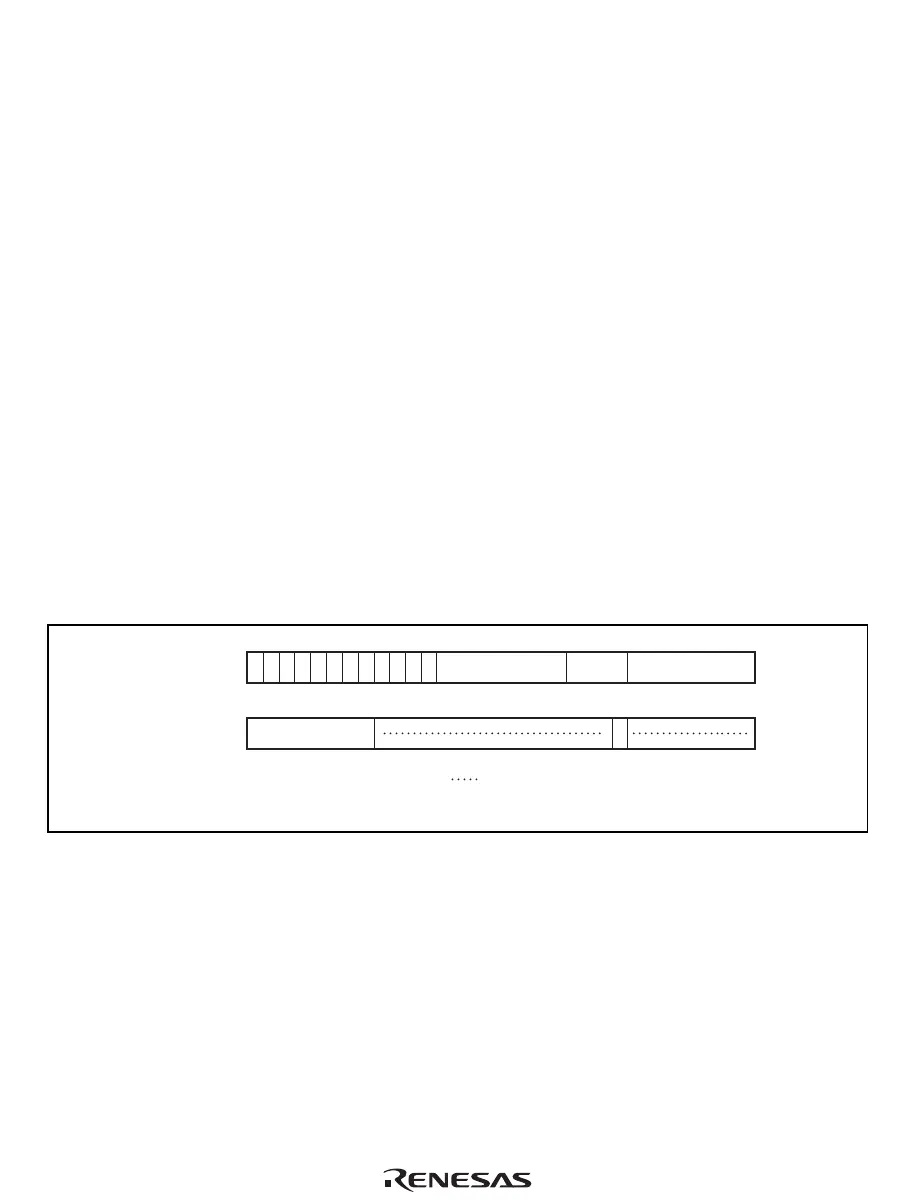

3. PMB data array read

When memory reading is performed while bits 31 to 20 in the address field are specified as

H'F71 which indicates the PMB data array and bits 11 to 8 in the address field as an entry, bits

31 to 24 in the data field are read as PPN, bit 9 in the data field as UB, bit 8 in the data field as

V, bits 7 and 4 in the data field as SZ, bit 3 in the data field as C, and bit 0 in the data field as

WT.

4. PMB data array write

When memory writing is performed while bits 31 to 20 in the address field are specified as

H'F71 which indicates the PMB data array and bits 11 to 8 in the address field as an entry, and

bits 31 to 24 in the data field are specified as PPN, bit 9 in the data field as UB, bit 8 in the

data field as V, bits 7 and 4 in the data field as SZ, bit 3 in the data field as C, and bit 0 in the

data field as WT, data is written to the specified entry.

Address field

Data field

VPN:

V:

E:

Physical page number

Validity bit

Entry

:

Reserved bits

(write value should be 0

and read value is undefined )

31 0

V

8

8

7

VPN

31 1920 0

11110 0001101 00E

2324

12

11

00000 00000000 0

Figure 7.18 Memory-Mapped PMB Address Array

Loading...

Loading...