Rev. 1.50, 10/04, page 41 of 448

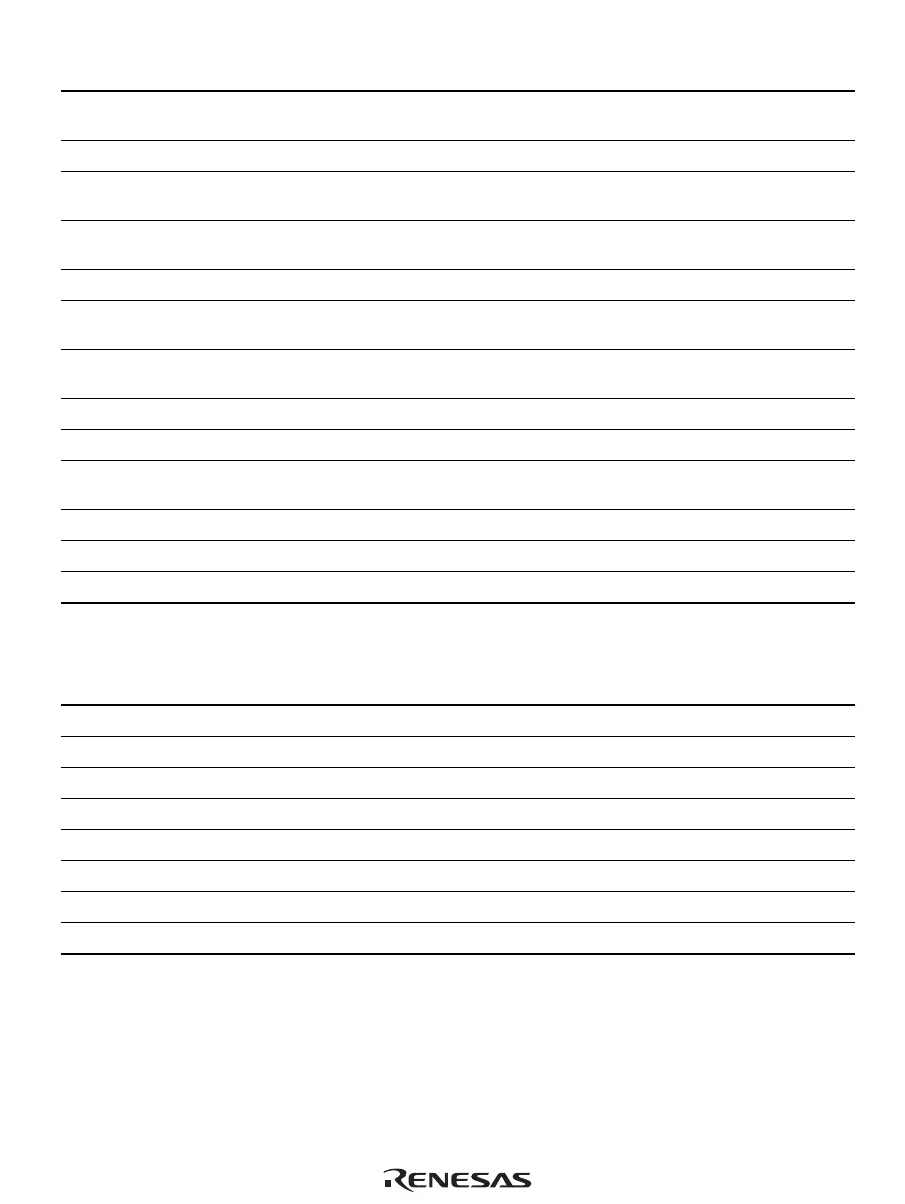

Table 3.11 Floating-Point Double-Precision Instructions

Instruction Operation Instruction Code Privileged T Bit New

FABS DRn DRn & H'7FFF FFFF FFFF

FFFF → DRn

1111nnn001011101

— — —

FADD DRm,DRn DRn + DRm → DRn

1111nnn0mmm00000

— — —

FCMP/EQ DRm,DRn When DRn = DRm, 1 → T

Otherwise, 0 → T

1111nnn0mmm00100

— Comparison

result

—

FCMP/GT DRm,DRn When DRn > DRm, 1 → T

Otherwise, 0 → T

1111nnn0mmm00101

— Comparison

result

—

FDIV DRm,DRn DRn /DRm → DRn

1111nnn0mmm00011

— — —

FCNVDS DRm,FPUL double_to_ float(DRm) →

FPUL

1111mmm010111101

— — —

FCNVSD FPUL,DRn float_to_ double (FPUL) →

DRn

1111nnn010101101

— — —

FLOAT FPUL,DRn (float)FPUL → DRn

1111nnn000101101

— — —

FMUL DRm,DRn DRn *DRm → DRn

1111nnn0mmm00010

— — —

FNEG DRn DRn ^ H'8000 0000 0000

0000 → DRn

1111nnn001001101

— — —

FSQRT DRn √DRn → DRn

1111nnn001101101

— — —

FSUB DRm,DRn DRn – DRm → DRn

1111nnn0mmm00001

— — —

FTRC DRm,FPUL (long) DRm → FPUL

1111mmm000111101

— — —

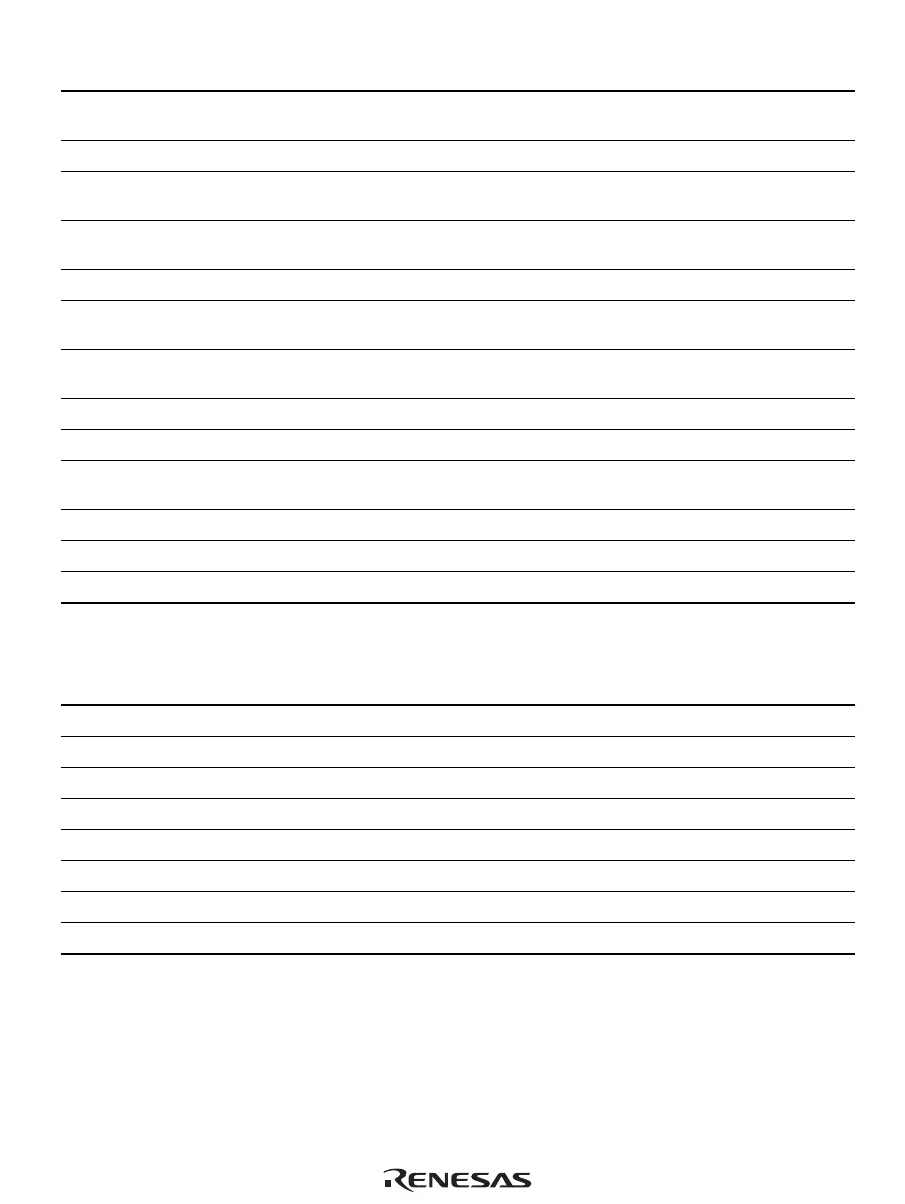

Table 3.12 Floating-Point Control Instructions

Instruction Operation Instruction Code Privileged T Bit New

LDS Rm,FPSCR Rm → FPSCR

0100mmmm01101010

— — —

LDS Rm,FPUL Rm → FPUL

0100mmmm01011010

— — —

LDS.L @Rm+,FPSCR (Rm) → FPSCR, Rm+4 → Rm

0100mmmm01100110

— — —

LDS.L @Rm+,FPUL (Rm) → FPUL, Rm+4 → Rm

0100mmmm01010110

— — —

STS FPSCR,Rn FPSCR → Rn

0000nnnn01101010

— — —

STS FPUL,Rn FPUL → Rn

0000nnnn01011010

— — —

STS.L FPSCR,@-Rn Rn – 4 → Rn, FPSCR → (Rn)

0100nnnn01100010

— — —

STS.L FPUL,@-Rn Rn – 4 → Rn, FPUL → (Rn)

0100nnnn01010010

— — —

Loading...

Loading...