Rev. 1.50, 10/04, page 37 of 448

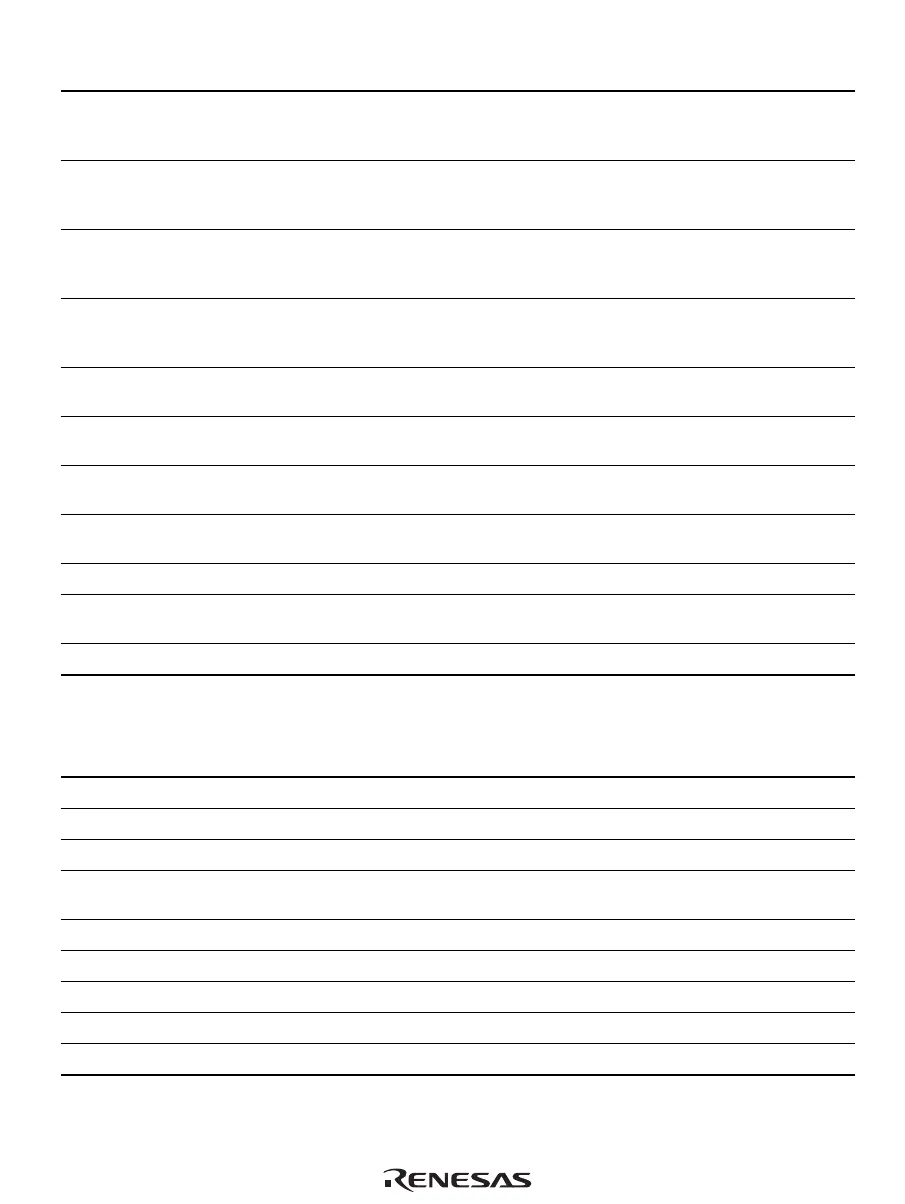

Table 3.8 Branch Instructions

Instruction Operation Instruction Code Privileged T Bit New

BF label When T = 0, disp × 2 + PC +

4 → PC

When T = 1, nop

10001011dddddddd

— — —

BF/S label Delayed branch; when T = 0,

disp × 2 + PC + 4 → PC

When T = 1, nop

10001111dddddddd

— — —

BT label When T = 1, disp × 2 + PC +

4 → PC

When T = 0, nop

10001001dddddddd

— — —

BT/S label Delayed branch; when T = 1,

disp × 2 + PC + 4 → PC

When T = 0, nop

10001101dddddddd

— — —

BRA label Delayed branch, disp × 2 +

PC + 4 → PC

1010dddddddddddd

— — —

BRAF Rn Delayed branch, Rn + PC + 4 →

PC

0000nnnn00100011

— — —

BSR label Delayed branch, PC + 4 → PR,

disp × 2 + PC + 4 → PC

1011dddddddddddd

— — —

BSRF Rn Delayed branch, PC + 4 → PR,

Rn + PC + 4 → PC

0000nnnn00000011

— — —

JMP @Rn Delayed branch, Rn → PC

0100nnnn00101011

— — —

JSR @Rn Delayed branch, PC + 4 → PR,

Rn → PC

0100nnnn00001011

— — —

RTS Delayed branch, PR → PC

0000000000001011

— — —

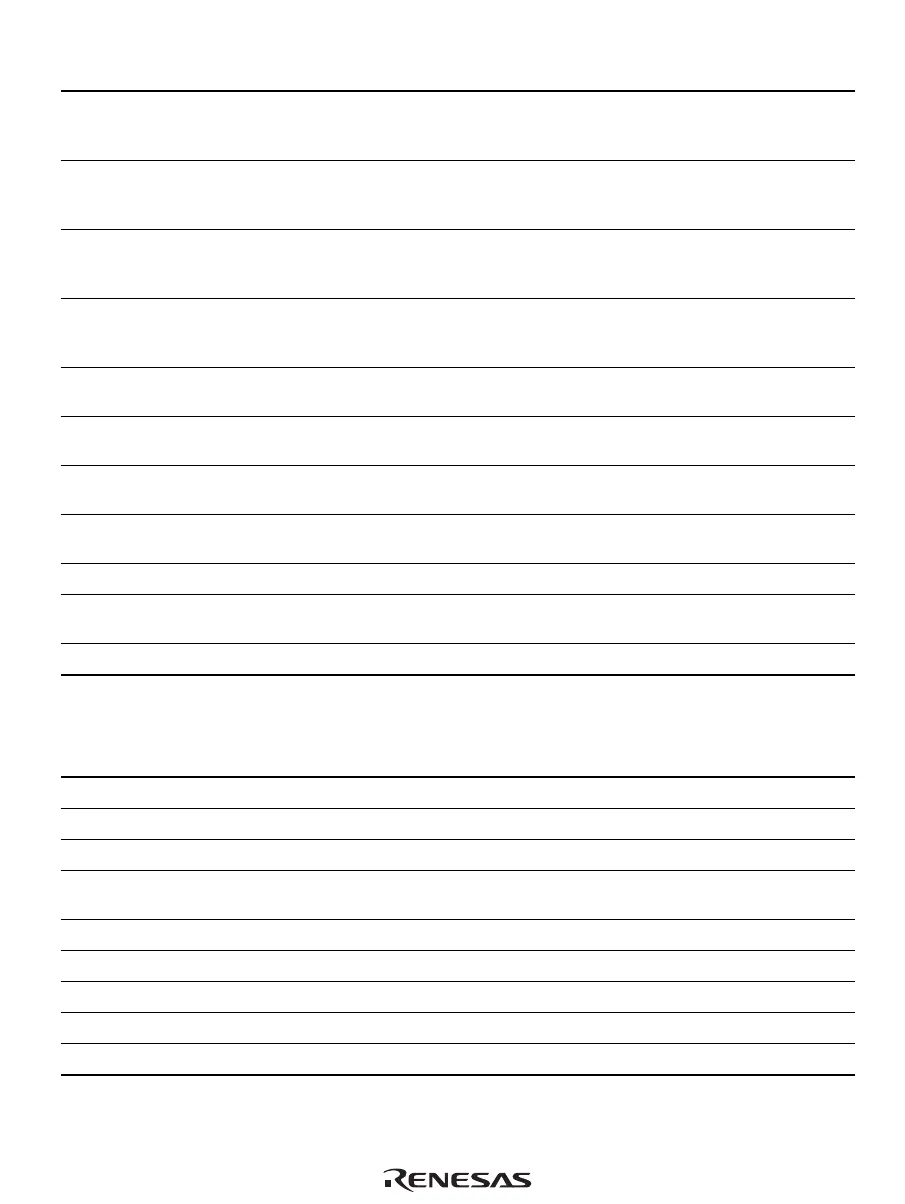

Table 3.9 System Control Instructions

Instruction Operation Instruction Code Privileged T Bit New

CLRMAC 0 → MACH, MACL

0000000000101000

— — —

CLRS 0 → S

0000000001001000

— — —

CLRT 0 → T

0000000000001000

— 0 —

ICBI @Rn Invalidates instruction cache block

indicated by logical address

0000nnnn11100011

New

LDC Rm,SR Rm → SR

0100mmmm00001110

Privileged LSB —

LDC Rm,GBR Rm → GBR

0100mmmm00011110

— — —

LDC Rm,VBR Rm → VBR

0100mmmm00101110

Privileged — —

LDC Rm,SGR Rm → SGR

0100mmmm00111010

Privileged — —

LDC Rm,SSR Rm → SSR

0100mmmm00111110

Privileged — —

Loading...

Loading...