Rev. 1.50, 10/04, page 199 of 448

9.4 L Memory Protective Functions

The SH-4A implements the following protective functions to the L memory by using the on-chip

memory access mode bit (RMD) and the on-chip memory protection enable bit (RP) in the on-chip

memory control register (RAMCR).

• Protective functions for access from the CPU and FPU

When RAMCR.RMD = 0, and the L memory is accessed in user mode, it is determined to be

an address error exception.

When MMUCR.AT = 1 and RAMCR.RP = 1, MMU exception and address error exception are

checked in the L memory area which is a part of area P4 as with the area P0/P3/U0.

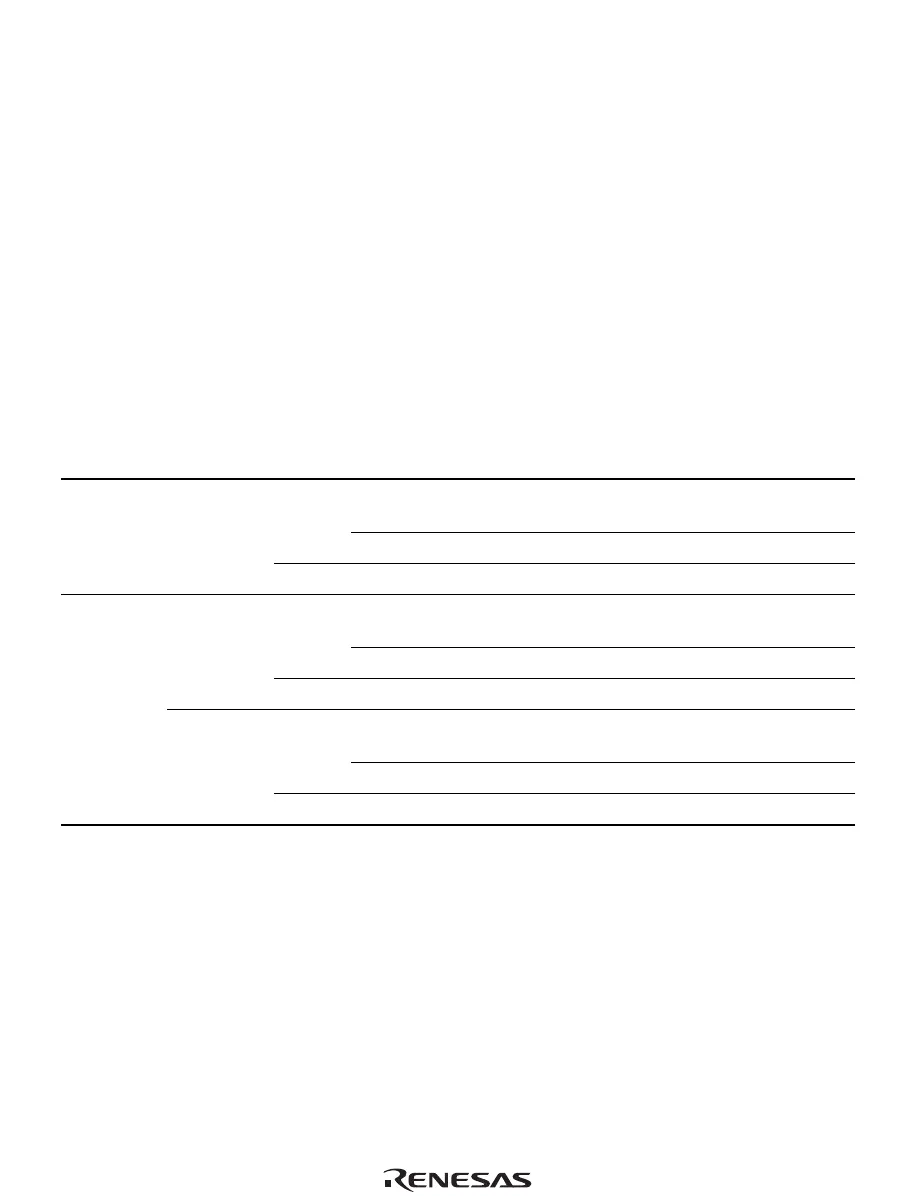

The above descriptions are summarized in table 9.4.

Table 9.4 Protective Function Exceptions to Access L Memory

MMUCR.AT RAMCR.RP SR.MD RAMCR. RMD

Always Occurring

Exceptions

Possibly Occurring

Exceptions

0 Address error

exception

—

0

1 — —

0 *

1 * — —

0 Address error

exception

— 0

1 — —

0

1 * — —

0 Address error

exception

— 0

1 — MMU exception

1

1

1 * — MMU exception

[Legend] *: Don't care

Loading...

Loading...