Rev. 1.50, 10/04, page 318 of 448

10.1.68 SHLRn (n bits Shift Logical Right): Shift Instruction

Format Operation Instruction Code Cycle T Bit

SHLR2 Rn Rn>>2 → Rn 0100nnnn00001001 1 —

SHLR8 Rn Rn>>8 → Rn 0100nnnn00011001 1 —

SHLR16 Rn Rn>>16 → Rn 0100nnnn00101001 1 —

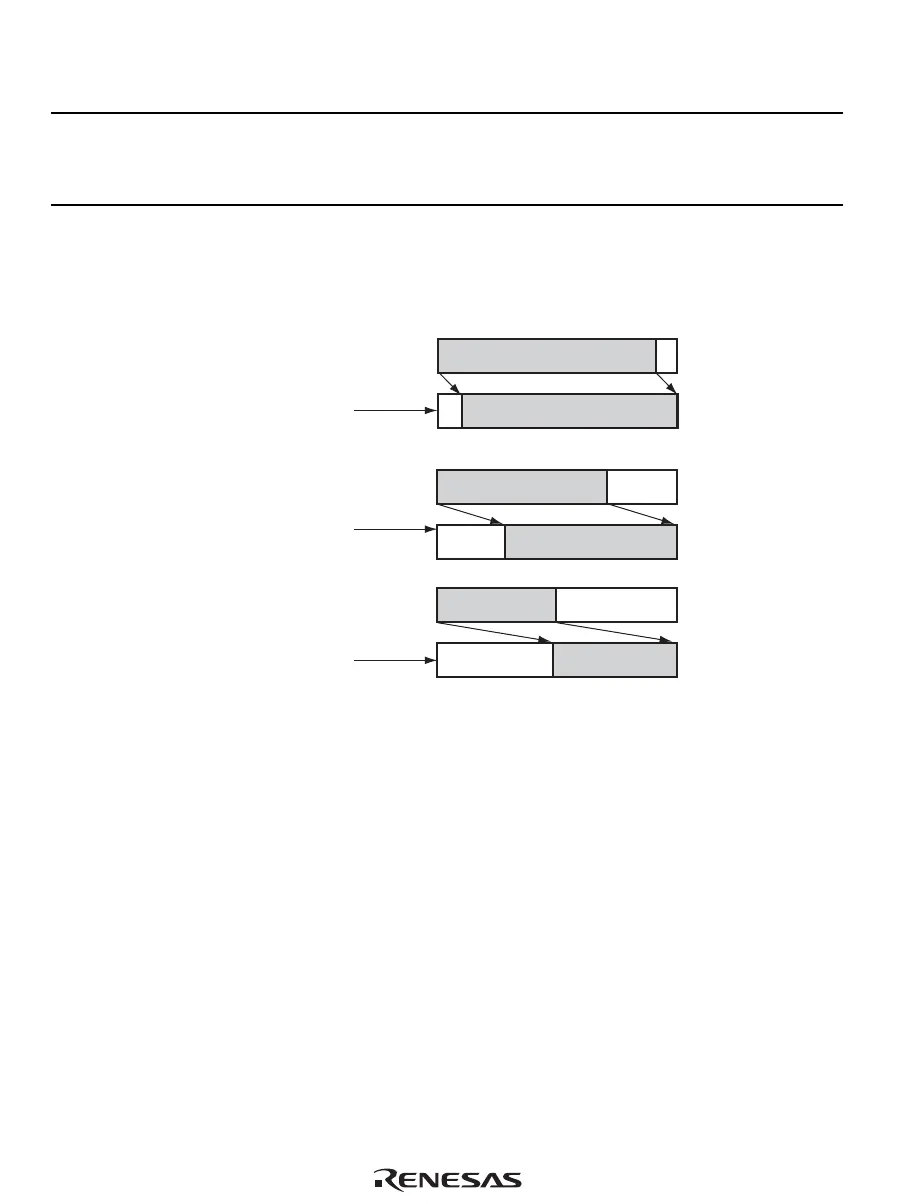

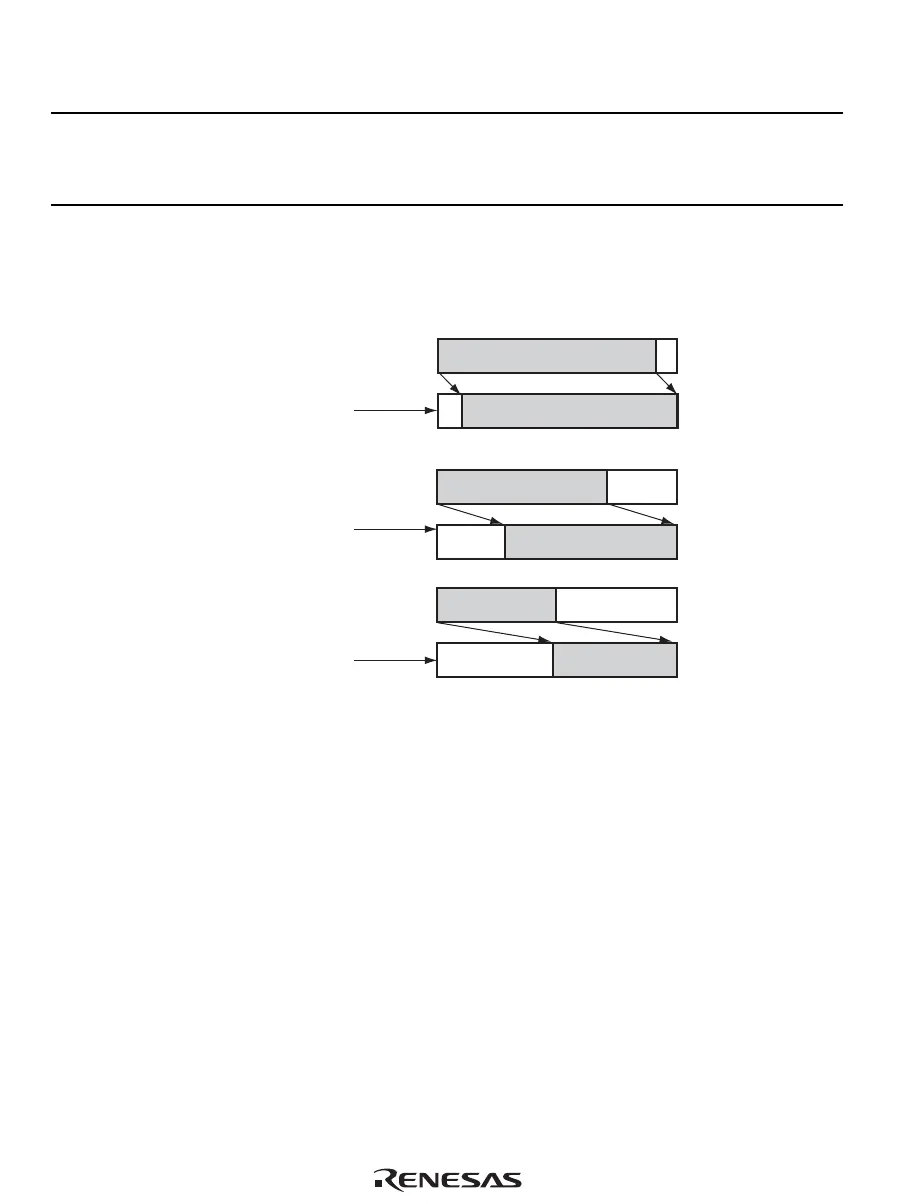

Description: This instruction logically shifts the contents of general register Rn 2, 8, or 16 bits to

the right, and stores the result in Rn. The bits shifted out of the operand are discarded.

MSB LSB

0

SHLR8

SHLR16

MSB LSB

0

MSB LSB

0

SHLR2

Notes: None

Loading...

Loading...