Rev. 1.50, 10/04, page 159 of 448

Section 8 Caches

The SH-4A has an on-chip 32-Kbyte instruction cache (IC) for instructions and an on-chip 32-

Kbyte operand cache (OC) for data.

Note: For the size of instruction cache and operand cache, see the hardware manual of the target

product. This manual describes the 32-Kbyte case for each cache memory.

8.1 Features

The features of the cache are given in table 8.1.

The SH-4A supports two 32-byte store queues (SQs) to perform high-speed writes to external

memory. The features of the store queues are given in table 8.2.

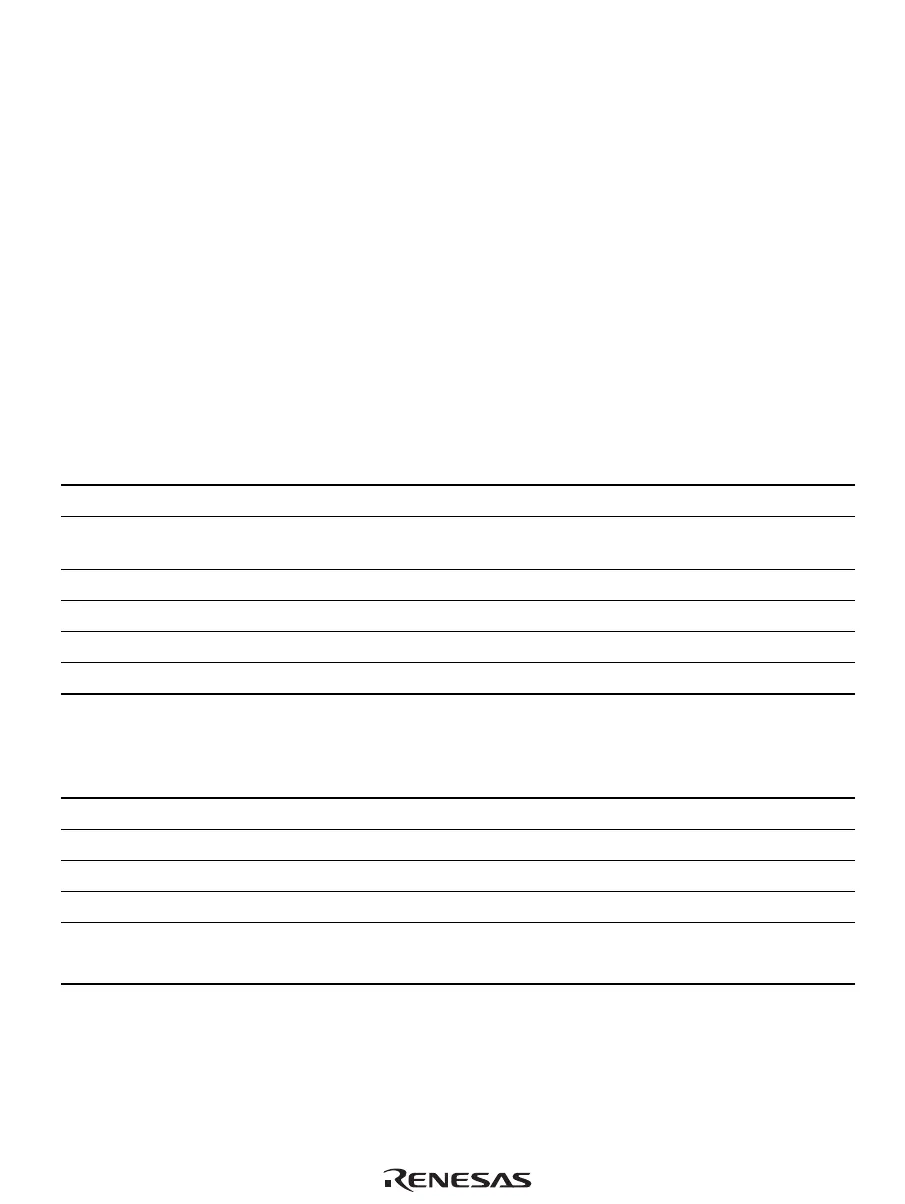

Table 8.1 Cache Features

Item Instruction Cache Operand Cache

Capacity 32-Kbyte cache 32-Kbyte cache

Type 4-way set-associative, virtual

address index/physical address tag

4-way set-associative, virtual

address index/physical address tag

Line size 32 bytes 32 bytes

Entries 256 entries/way 256 entries/way

Write method Copy-back/write-through selectable

Replacement method LRU (least-recently-used) algorithm LRU (least-recently-used) algorithm

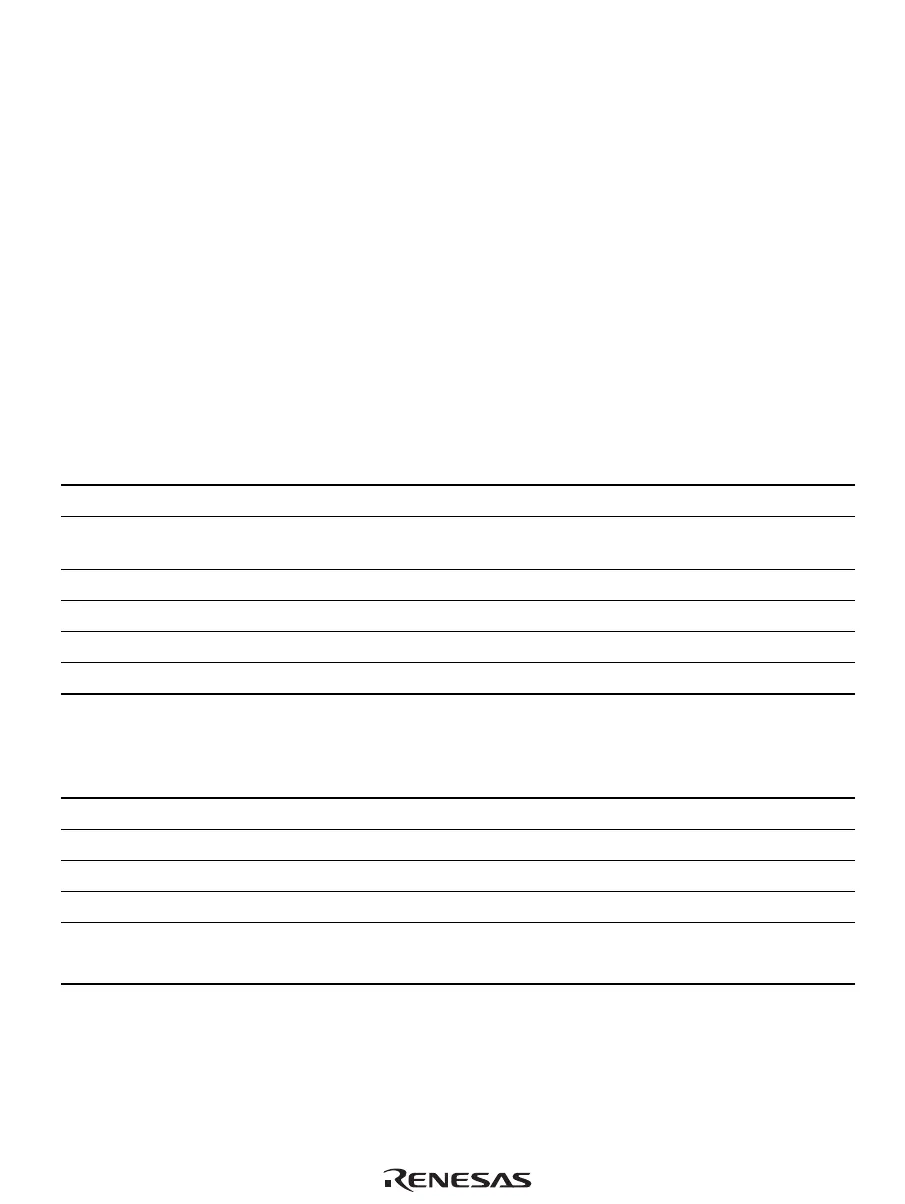

Table 8.2 Store Queue Features

Item Store Queues

Capacity 32 bytes × 2

Addresses H'E000 0000 to H'E3FF FFFF

Write Store instruction (1-cycle write)

Write-back Prefetch instruction (PREF instruction)

Access right When MMU is disabled: Determined by SQMD bit in MMUCR

When MMU is enabled: Determined by PR for each page

Loading...

Loading...