Rev. 1.50, 10/04, page 47 of 448

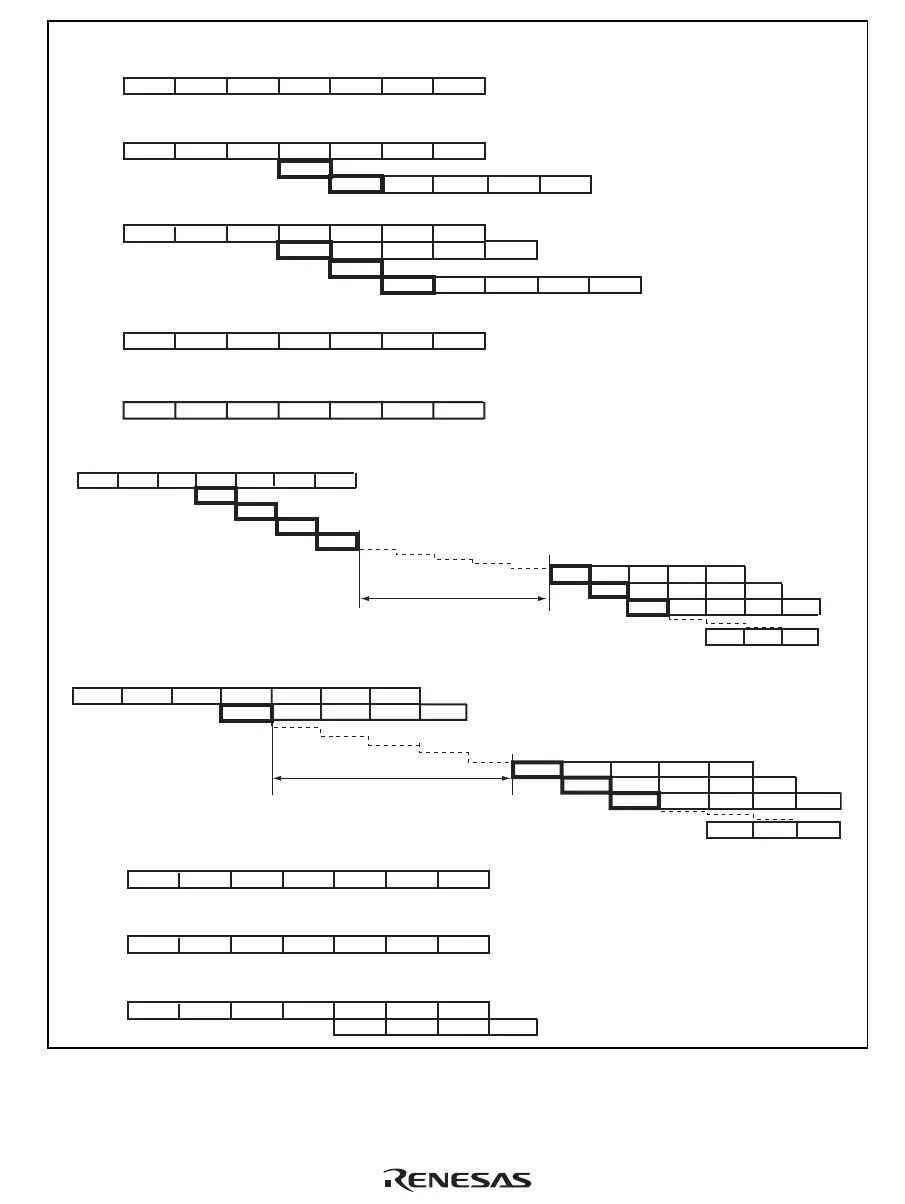

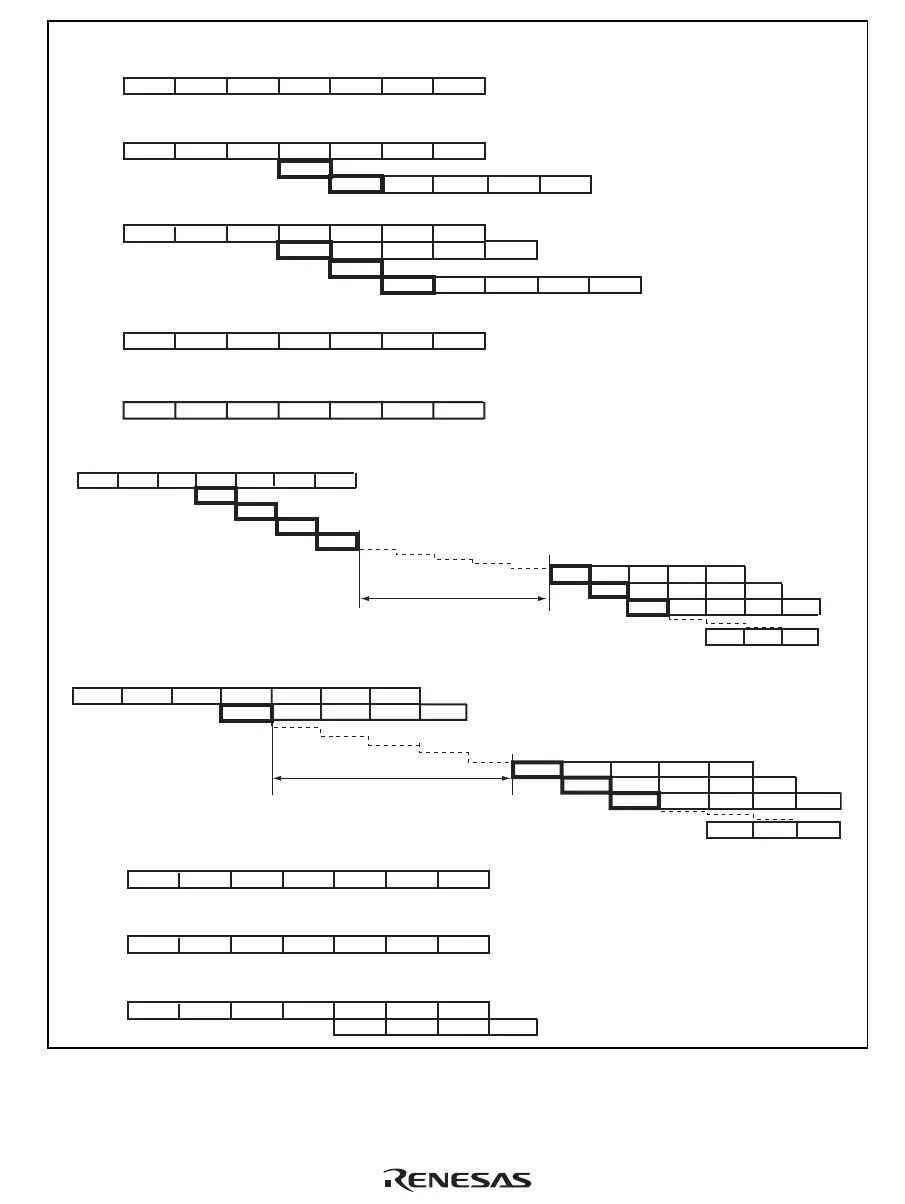

(3-1) Load/store: 1 issue cycle

I1 I2 ID S1 S2 S3

WB

I1 I2 ID S1 S2 S3

WB

(3-2) AND.B, OR.B, XOR.B, TST.B: 3 issue cycles

I1 I2 ID S1 S2 S3

WB

(3-3) TAS.B: 4 issue cycles

(3-4) PREF, OCBI, OCBP, OCBWB, MOVCA.L, SYNCO: 1 issue cycle

MOV.[BWL], MOV.[BWL] @(d,GBR)

I1 I2 ID S1 S2 S3

WB

E2s2 E3s3

E1s1

(3-5) LDTLB: 1 issue cycle

I1 I2 ID

WB

(3-6) ICBI: 8 issue cycles + 5 cycles + 3 branch cycle

(3-7) PREFI: 5 issue cycles + 5 cycles + 3 branch cycle

(3-8) MOVLI.L: 1 issue cycle

I1 I2 ID S1 S2 S3

WB

(3-9) MOVCO.L: 1 issue cycle

I1 I2 ID S1 S2 S3

WB

(3-10) MOVUA.L: 2 issue cycles

I1 I2 ID S1 S2 S3 WB

S1 S2 S3

WB

(Branch to the next instruction of ICBI.)

E2S2 E3S3 WBE1S1ID

ID

E2S2 E3S3

WBE1S1

E2S2 E3S3 WB

E1S1

ID

ID

ID

I1 I2 ID s1 s2 s3

WB

E1s1

E1s1

E1s1

E2s2

E2s2

E2s2

E3s3

E3s3

E3s3

WB

WB

WB

(I1)

(ID)(I2)

ID

ID

ID

ID

ID

ID

ID

5 cycles (min.)

I1 I2 ID s1 s2 s3

WB

E1s1 E2s2 E3s3 WB

ID

E1s1

E1s1

E1s1

E2s2

E2s2

E2s2

E3s3

E3s3

E3s3

WB

WB

WB

(I1)

(ID)(I2)

ID

ID

ID

(Branch to the next instruction of PREFI.)

5 cycles (min.)

Figure 4.2 Instruction Execution Patterns (3)

Loading...

Loading...