Rev. 1.50, 10/04, page 51 of 448

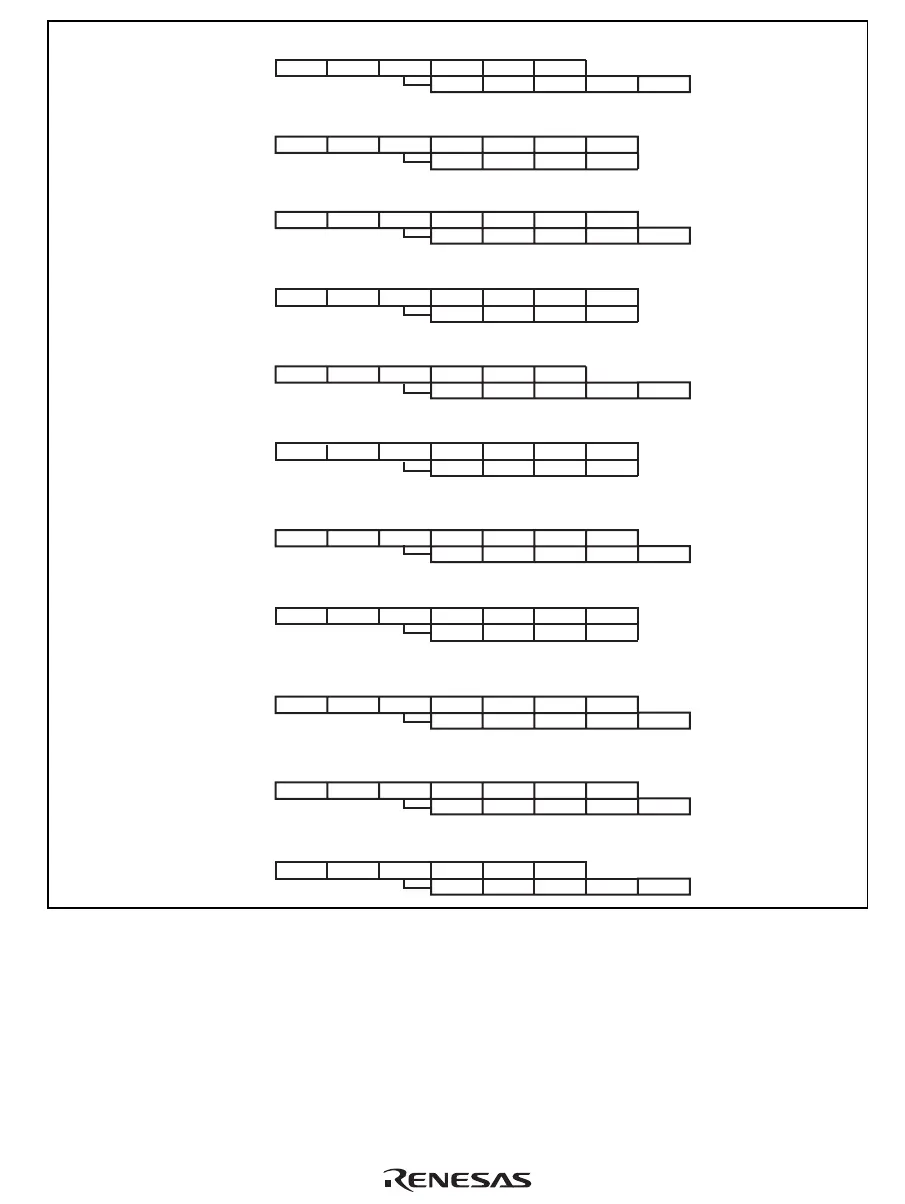

(6-1) LDS to FPUL: 1 issue cycle

I1 I2 ID s1 s2 s3

s1 s2 s3 WB

s1 s2 s3 WB

FS1 FS2 FS3 FS4

FS1 FS2 FS3 FS4

FS

FS1 FS2 FS3 FS4

FS1 FS2 FS3 FS4

FS1 FS2 FS3 FS4

FS

FS1 FS2 FS3 FS4 FS

FS1 FS2 FS3 FS4

FS1 FS2 FS3 FS4

FS

FS1 FS2 FS3 FS4

FS

(6-2) STS from FPUL: 1 issue cycle

(6-3) LDS.L to FPUL: 1 issue cycle

(6-4) STS.L from FPUL: 1 issue cycle

(6-5) LDS to FPSCR: 1 issue cycle

(6-6) STS from FPSCR: 1 issue cycle

(6-7) LDS.L to FPSCR: 1 issue cycle

(6-8) STS.L from FPSCR: 1 issue cycle

(6-9) FPU load/store instruction FMOV: 1 issue cycle

I1 I2

ID

I1 I2 ID S1 S2 S3 WB

S1 S2 S3

S1 S2 S3

WB

I1 I2 ID s1 s2

s3

I1 I2 ID WB

S1 S2 S3

WB

FS3

S1 S2 S3

WB

FS1 FS2 FS3 FS4 FS

s1 s2 s3

WB

I1 I2

ID

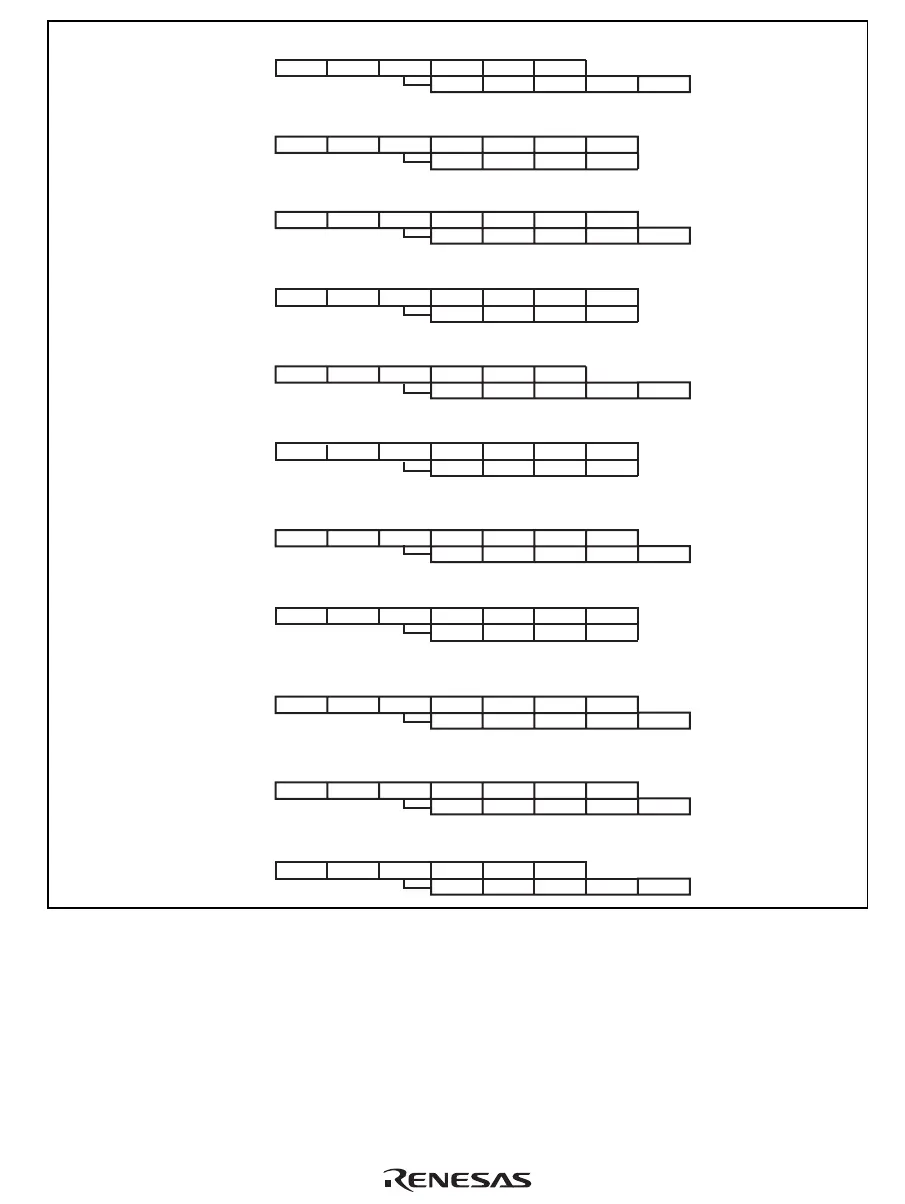

(6-10) FLDS: 1 issue cycle

I1 I2

ID

I1 I2

ID

I1 I2

ID

(6-11) FSTS: 1 issue cycle

I1 I2

ID

I1 I2

ID

FS1 FS2 FS4

FS

s1 s2

s3

Figure 4.2 Instruction Execution Patterns (7)

Loading...

Loading...