Rev. 1.50, 10/04, page 178 of 448

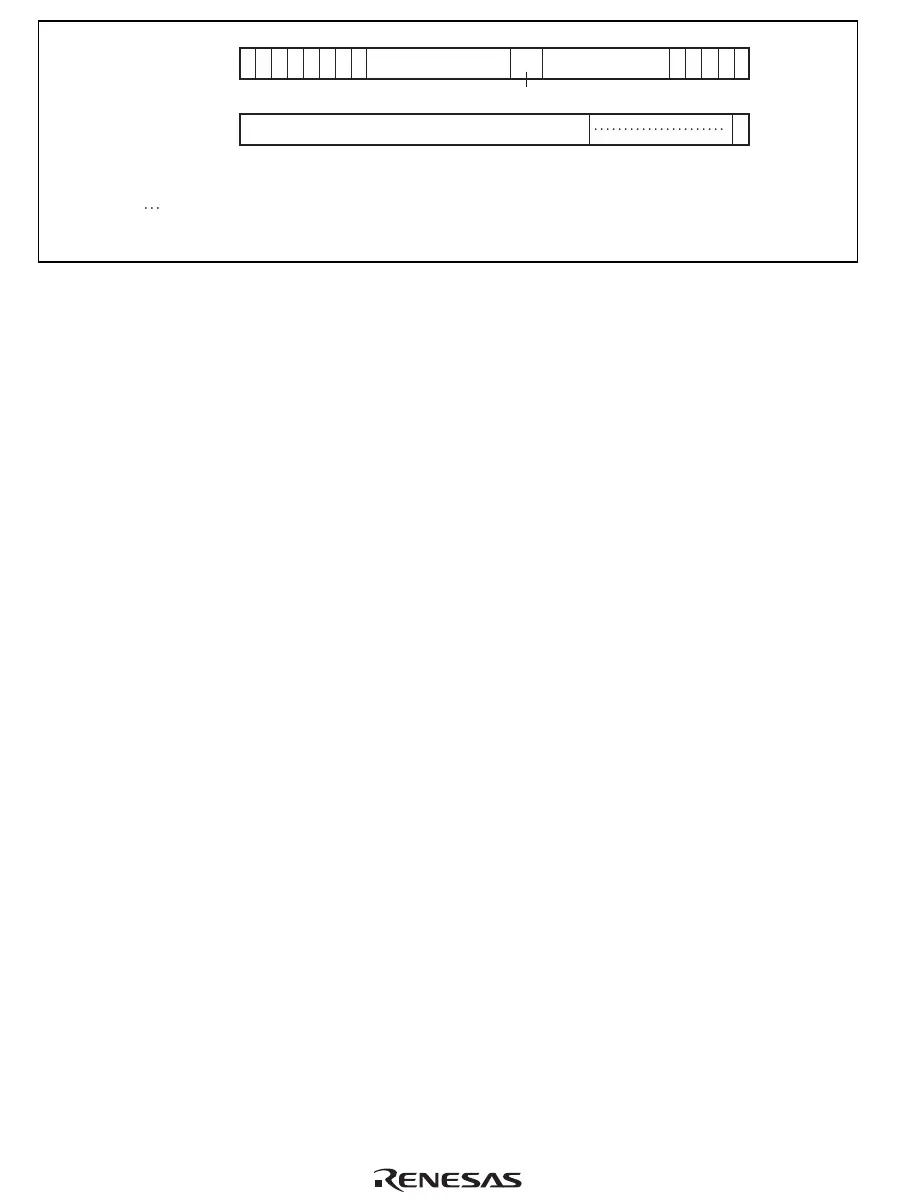

Address field

31 23 12 543210

11110000 0000

Entry

A

Data field

31 10 9 1 0

V

Tag

Way

V

A

24 131415

: Validity bit

: Association bit

:

Reserved bits

(write value should be 0 and read value is undefined )

: Don't care

*

*********

Figure 8.5 Memory-Mapped IC Address Array

8.6.2 IC Data Array

The IC data array is allocated to addresses H'F100 0000 to H'F1FF FFFF in the P4 area. A data

array access requires a 32-bit address field specification (when reading or writing) and a 32-bit

data field specification. The way and entry to be accessed are specified in the address field, and

the longword data to be written is specified in the data field.

In the address field, bits [31:24] have the value H'F1 indicating the IC data array, and the way is

specified by bits [14:13] and the entry by bits [12:5]. Address field bits [4:2] are used for the

longword data specification in the entry. As only longword access is used, 0 should be specified

for address field bits [1:0].

The data field is used for the longword data specification.

The following two kinds of operation can be used on the IC data array:

1. IC data array read

Longword data is read into the data field from the data specified by the longword specification

bits in the address field in the IC entry corresponding to the way and entry set in the address

field.

2. IC data array write

The longword data specified in the data field is written for the data specified by the longword

specification bits in the address field in the IC entry corresponding to the way and entry set in

the address field.

Loading...

Loading...