Rev. 1.50, 10/04, page 107 of 448

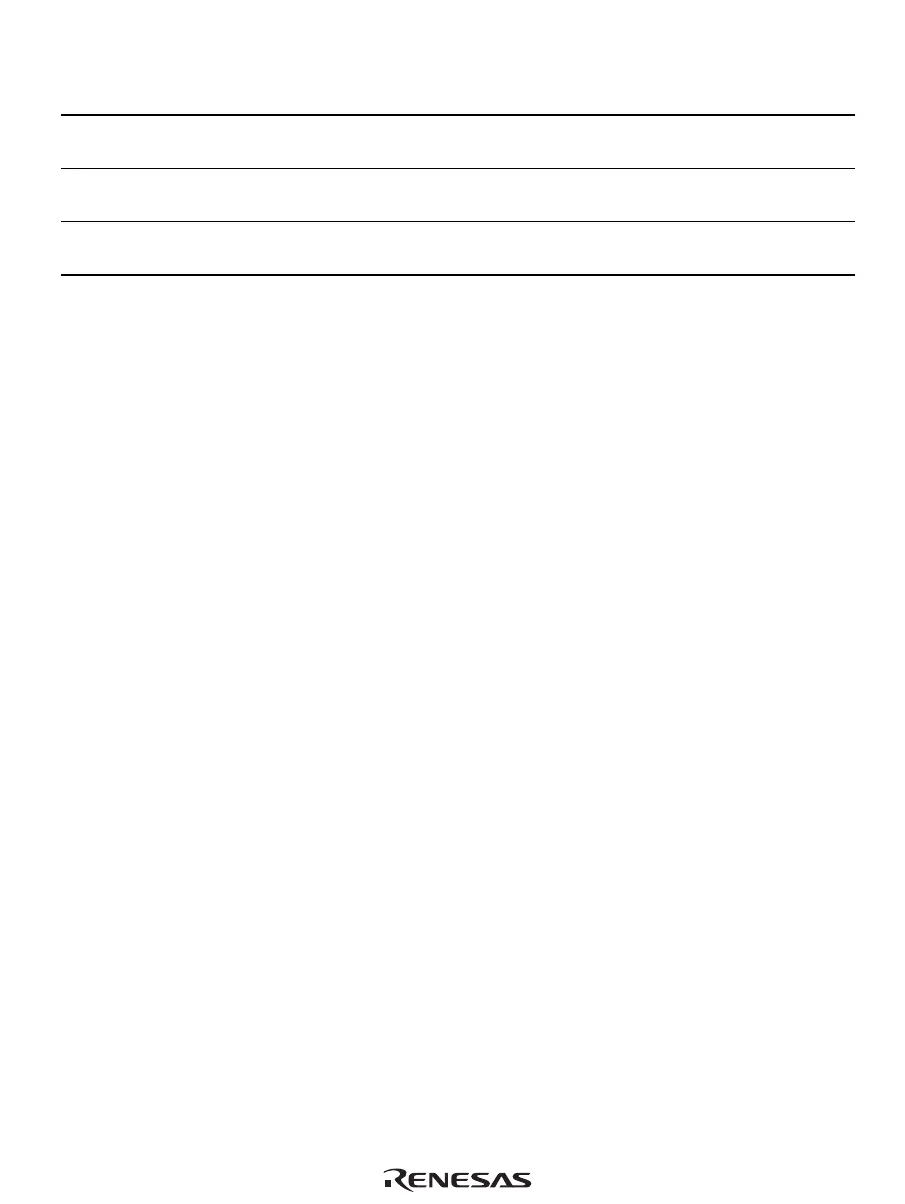

Table 6.3 Bit Allocation for FPU Exception Handling

Field Name

FPU

Error (E)

Invalid

Operation (V)

Division

by Zero (Z)

Overflow

(O)

Underflo

w (U)

Inexact

(I)

Cause FPU exception

cause field

Bit 17 Bit 16 Bit 15 Bit 14 Bit 13 Bit 12

Enable FPU exception

enable field

None Bit 11 Bit 10 Bit 9 Bit 8 Bit 7

Flag FPU exception

flag field

None Bit 6 Bit 5 Bit 4 Bit 3 Bit 2

6.3.3 Floating-Point Communication Register (FPUL)

Information is transferred between the FPU and CPU via FPUL. FPUL is a 32-bit system register

that is accessed from the CPU side by means of LDS and STS instructions. For example, to

convert the integer stored in general register R1 to a single-precision floating-point number, the

processing flow is as follows:

R1 → (LDS instruction) → FPUL → (single-precision FLOAT instruction) → FR1

Loading...

Loading...