Rev. 1.50, 10/04, page 189 of 448

9.2.1 On-Chip Memory Control Register (RAMCR)

RAMCR controls the protective functions in the L memory.

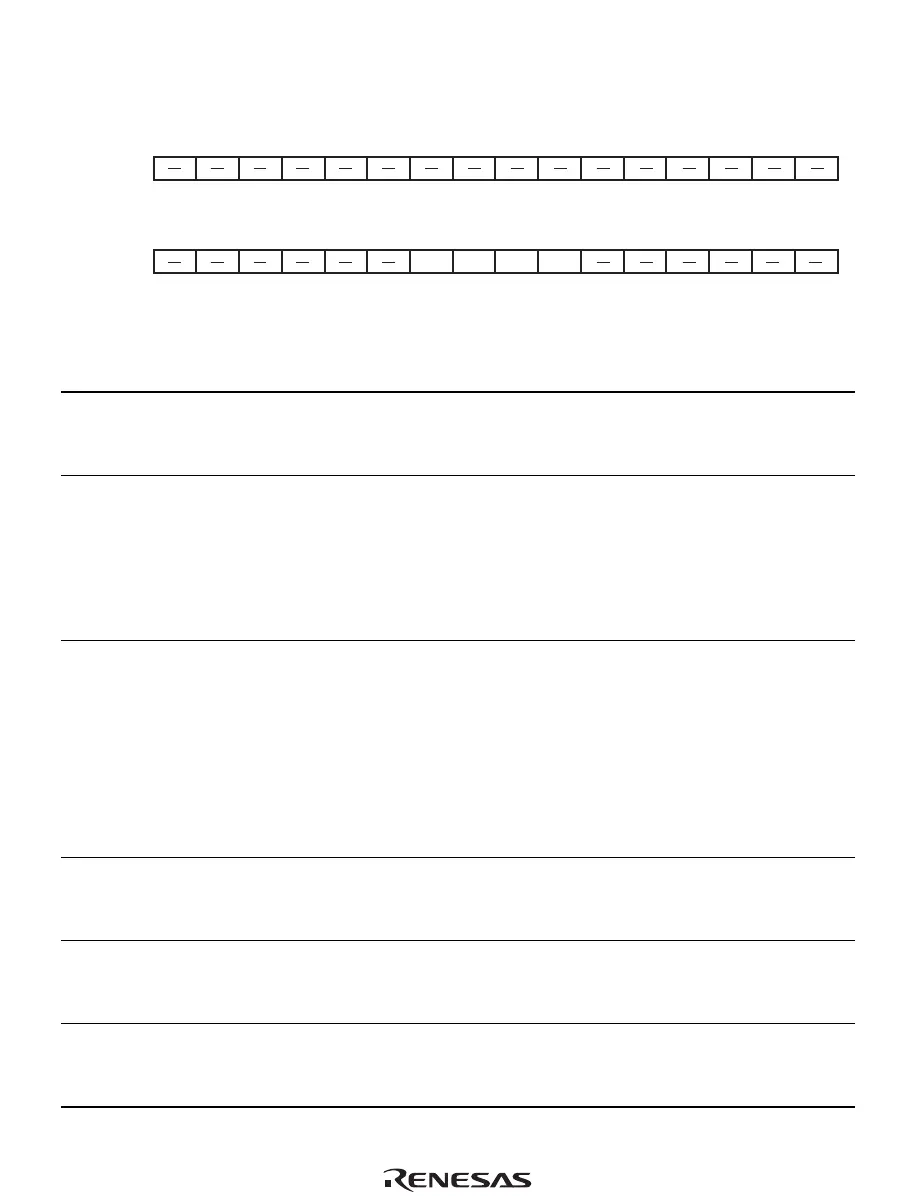

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Bit :

0000000000000000

RMD RP IC2W

OC2W

Initial value :

RRRRRRRRRRRRRRRR

R/W:

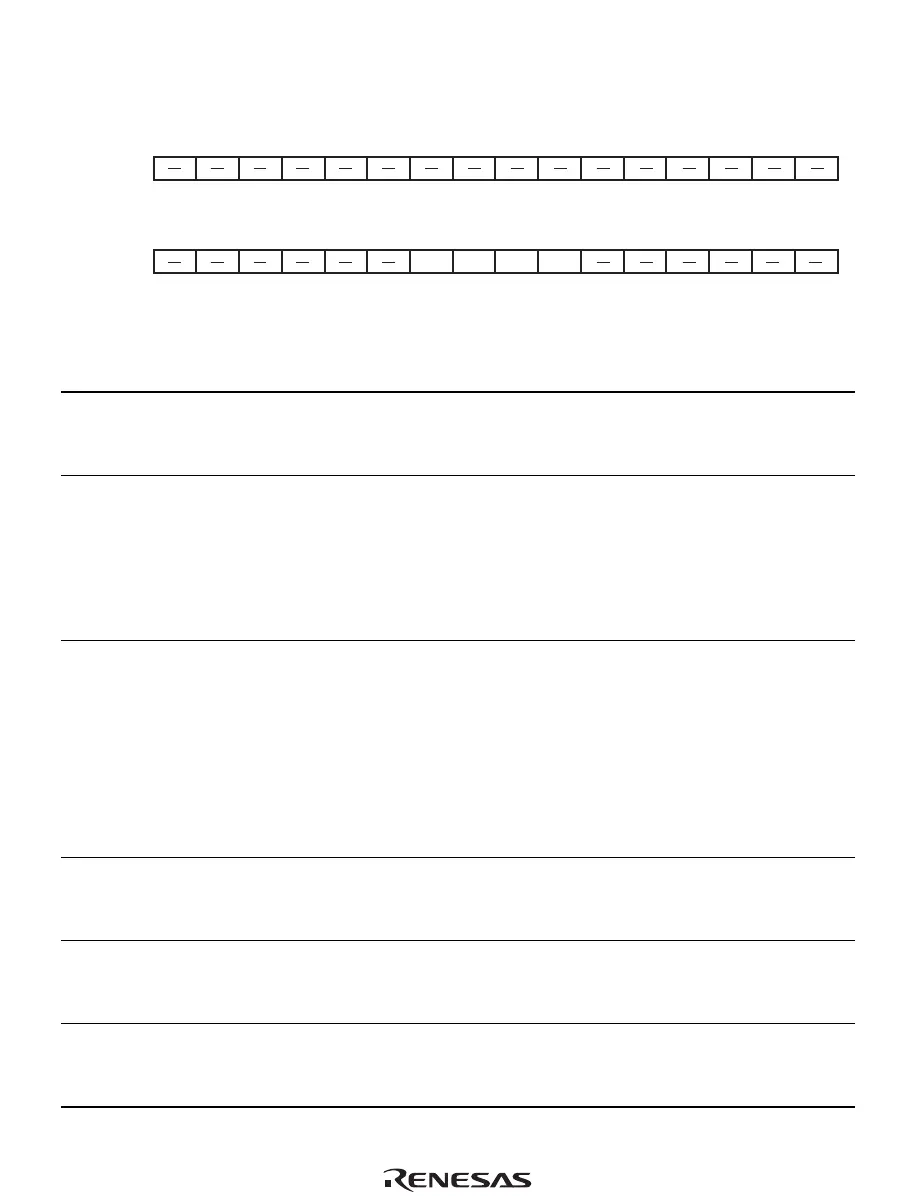

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1

0

Bit :

00000000

0

0000000

Initial value :

R R R R R R R/W R/W R/W R/W R R R R R R

R/W:

Bit Bit Name

Initial

Value R/W Description

31to10 — All 0 R Reserved

For read/write in these bits, refer to General

Precautions on Handling of Product.

9 RMD 0 R/W On-Chip Memory Access Mode

Specifies the right of access to the L memory from the

virtual address space.

0: An access in privileged mode is allowed.

(An address error exception occurs in user mode.)

1: An access in user/ privileged mode is allowed.

8 RP 0 R/W On-Chip Memory Protection Enable

Selects whether or not to use the protective functions

using ITLB and UTLB for accessing the L memory from

the virtual address space.

0: Protective functions are not used.

1: Protective functions are used.

For further details, refer to section 9.4, L Memory

Protective Functions.

7 IC2W 0 R/W IC Two-Way Mode

For further details, refer to section 8.4.3, IC Two-Way

Mode.

6 OC2W 0 R/W OC Two-Way Mode

For further details, refer to section 8.3.6, OC Two-Way

Mode.

5 to 0 — All 0 R Reserved

For read/write in these bits, refer to General

Precautions on Handling of Product.

Loading...

Loading...