Rev. 1.50, 10/04, page 165 of 448

8.2.2 Queue Address Control Register 0 (QACR0)

QACR0 specifies the area onto which store queue 0 (SQ0) is mapped when the MMU is disabled.

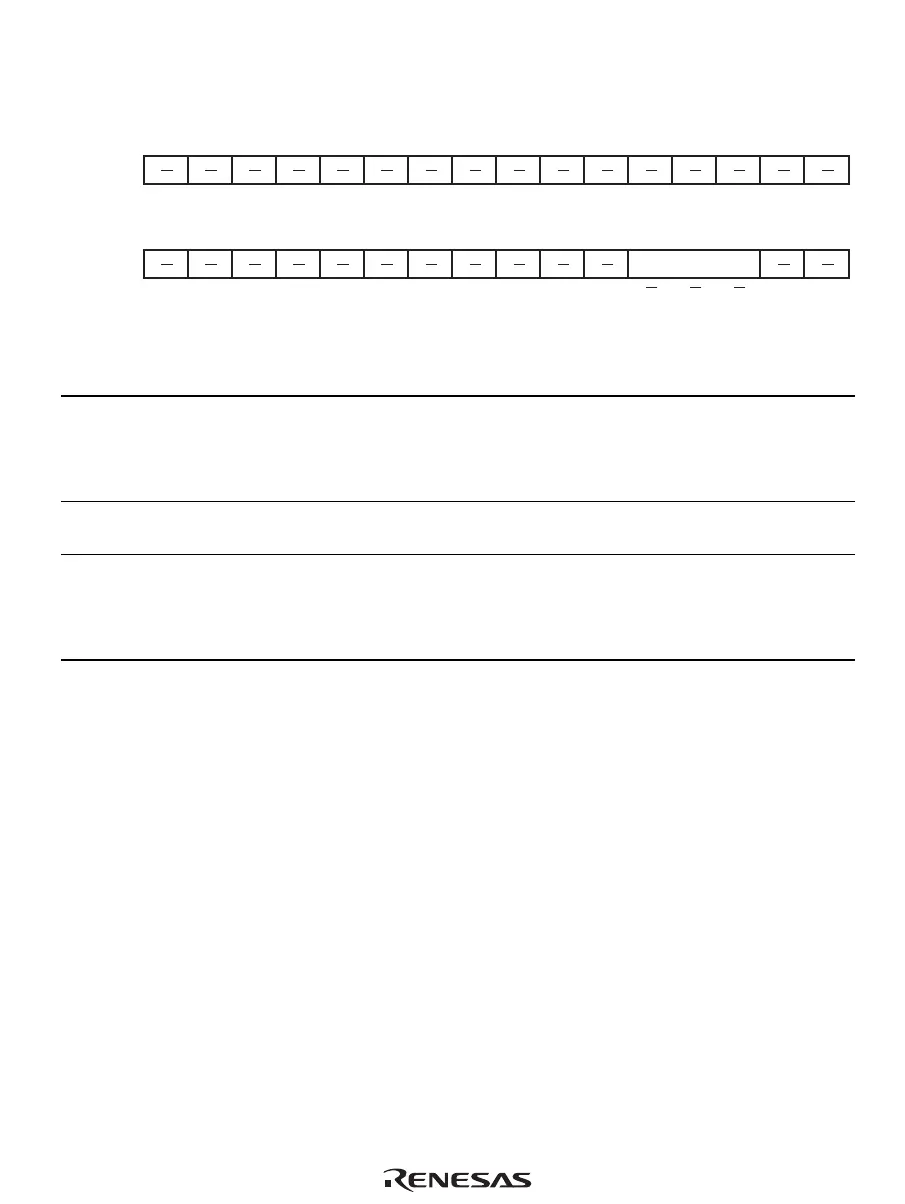

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Bit:

Initial value:

RRRRRRRRRRRRRRRR

0000000000000000

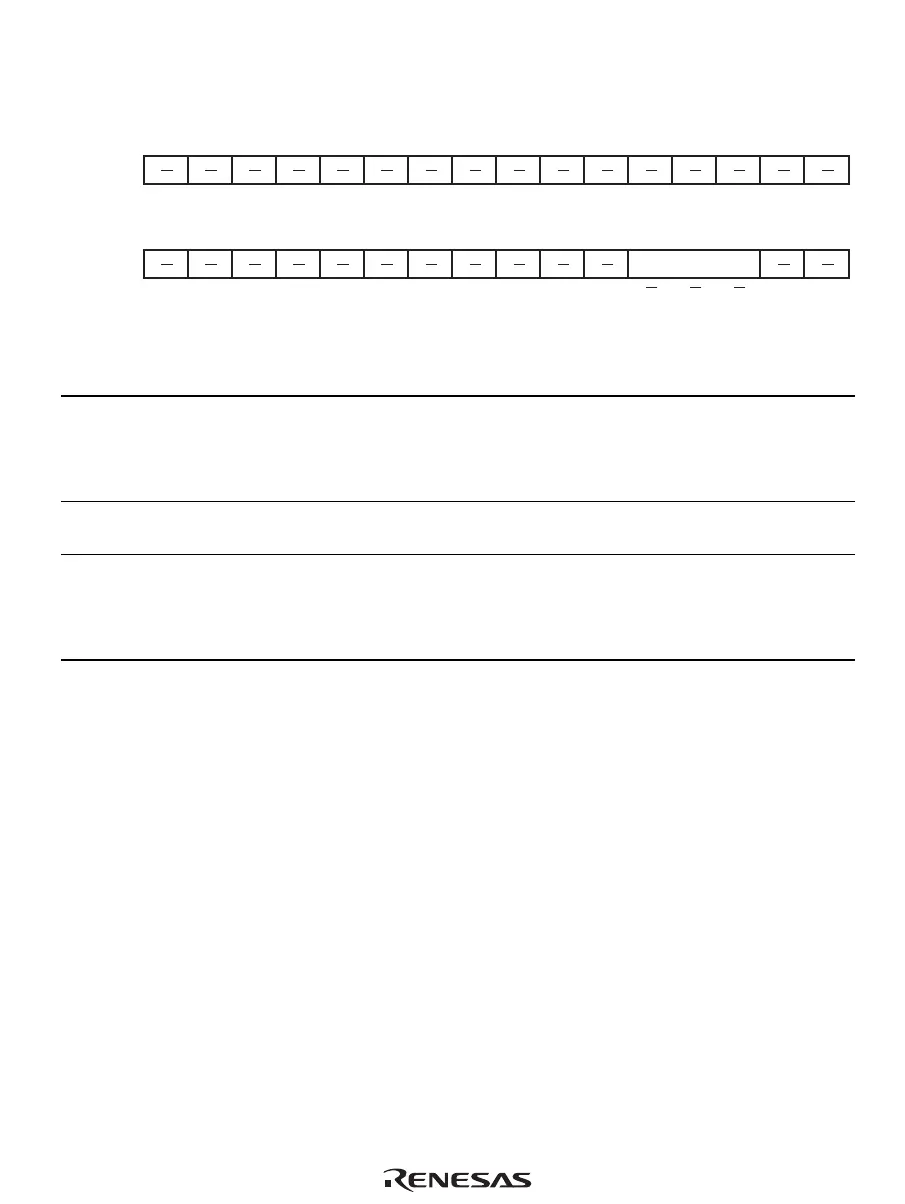

00000000000 00

R R R R R R R R R R R R/W R/W R/W R R

R/W:

Bit:

Initial value:

R/W:

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1

0

AREA0

Bit Bit Name

Initial

Value R/W Description

31 to 5 All 0 R Reserved

For details on reading from or writing to these bits, see

description in General Precautions on Handling of

Product.

4 to 2 AREA0 Undefined R/W When the MMU is disabled, these bits generate

physical address bits [28:26] for SQ0.

1, 0 All 0 R Reserved

For details on reading from or writing to these bits, see

description in General Precautions on Handling of

Product.

Loading...

Loading...