Rev. 1.50, 10/04, page 179 of 448

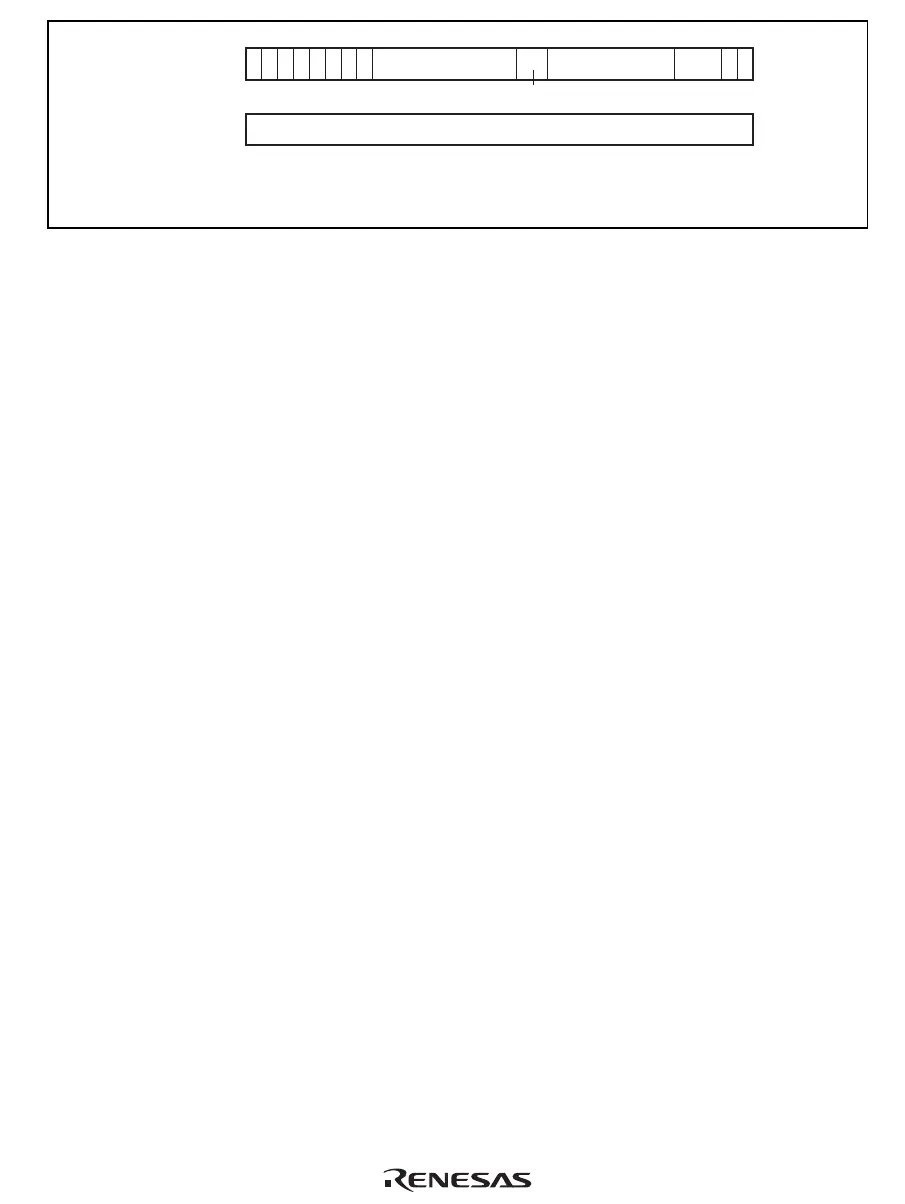

Address field

31 23 12 5 4 2 1 0

11110001 Entry L

Data field

31 0

Longword data

L

*

24 131415

: Longword specification bits

: Don't care

Way

00

*********

Figure 8.6 Memory-Mapped IC Data Array

8.6.3 OC Address Array

The OC address array is allocated to addresses H'F400 0000 to H'F4FF FFFF in the P4 area. An

address array access requires a 32-bit address field specification (when reading or writing) and a

32-bit data field specification. The way and entry to be accessed are specified in the address field,

and the write tag, U bit, and V bit are specified in the data field.

In the address field, bits [31:24] have the value H'F4 indicating the OC address array, and the way

is specified by bits [14:13] and the entry by bits [12:5]. The association bit (A bit) [3] in the

address field specifies whether or not association is performed when writing to the OC address

array. As only longword access is used, 0 should be specified for address field bits [1:0].

In the data field, the tag is indicated by bits [31:10], the U bit by bit [1], and the V bit by bit [0].

As the OC address array tag is 19 bits in length, data field bits [31:29] are not used in the case of a

write in which association is not performed. Data field bits [31:29] are used for the virtual address

specification only in the case of a write in which association is performed.

The following three kinds of operation can be used on the OC address array:

1. OC address array read

The tag, U bit, and V bit are read into the data field from the OC entry corresponding to the

way and entry set in the address field. In a read, associative operation is not performed

regardless of whether the association bit specified in the address field is 1 or 0.

2. OC address array write (non-associative)

The tag, U bit, and V bit specified in the data field are written to the OC entry corresponding to

the way and entry set in the address field. The A bit in the address field should be cleared to 0.

When a write is performed to a cache line for which the U bit and V bit are both 1, after write-

back of that cache line, the tag, U bit, and V bit specified in the data field are written.

Loading...

Loading...