Rev. 1.50, 10/04, page 134 of 448

7.3.3 Address Translation Method

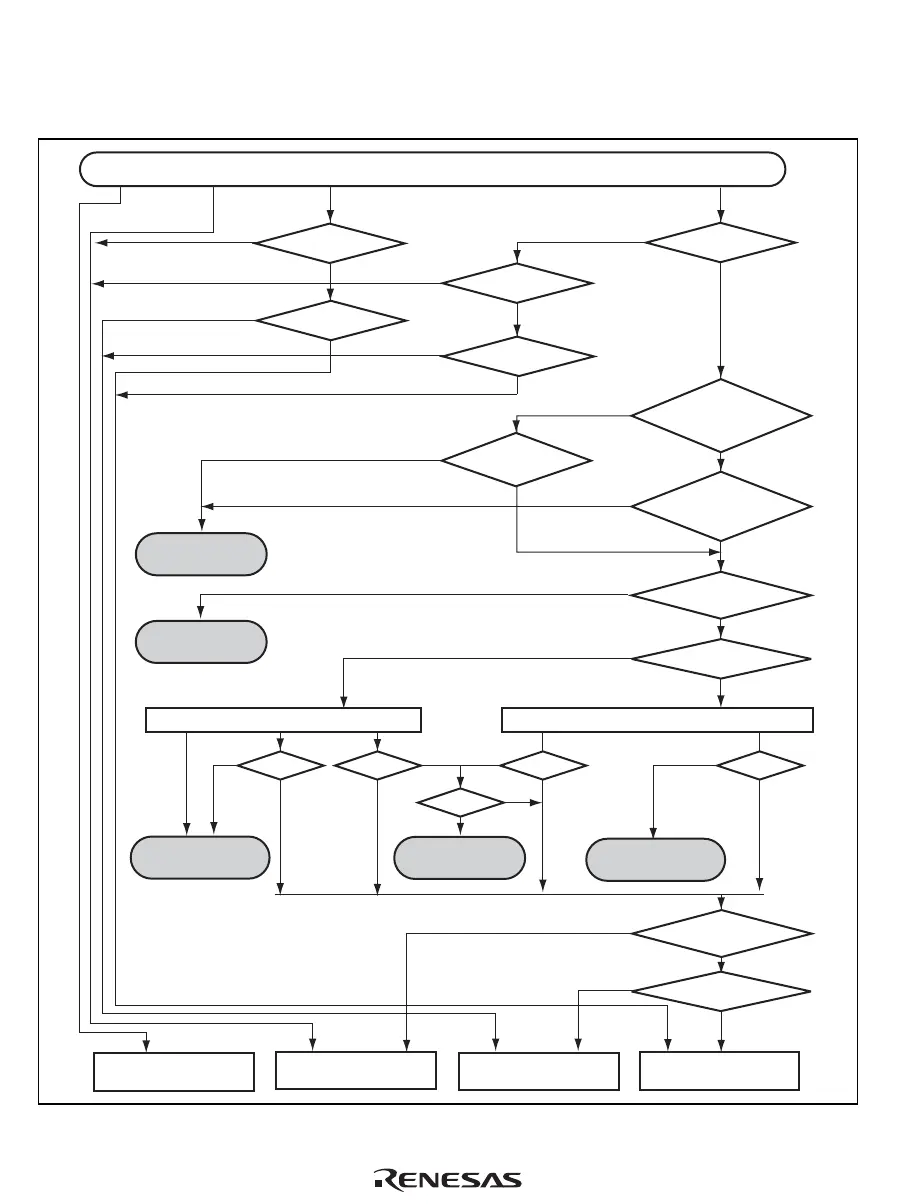

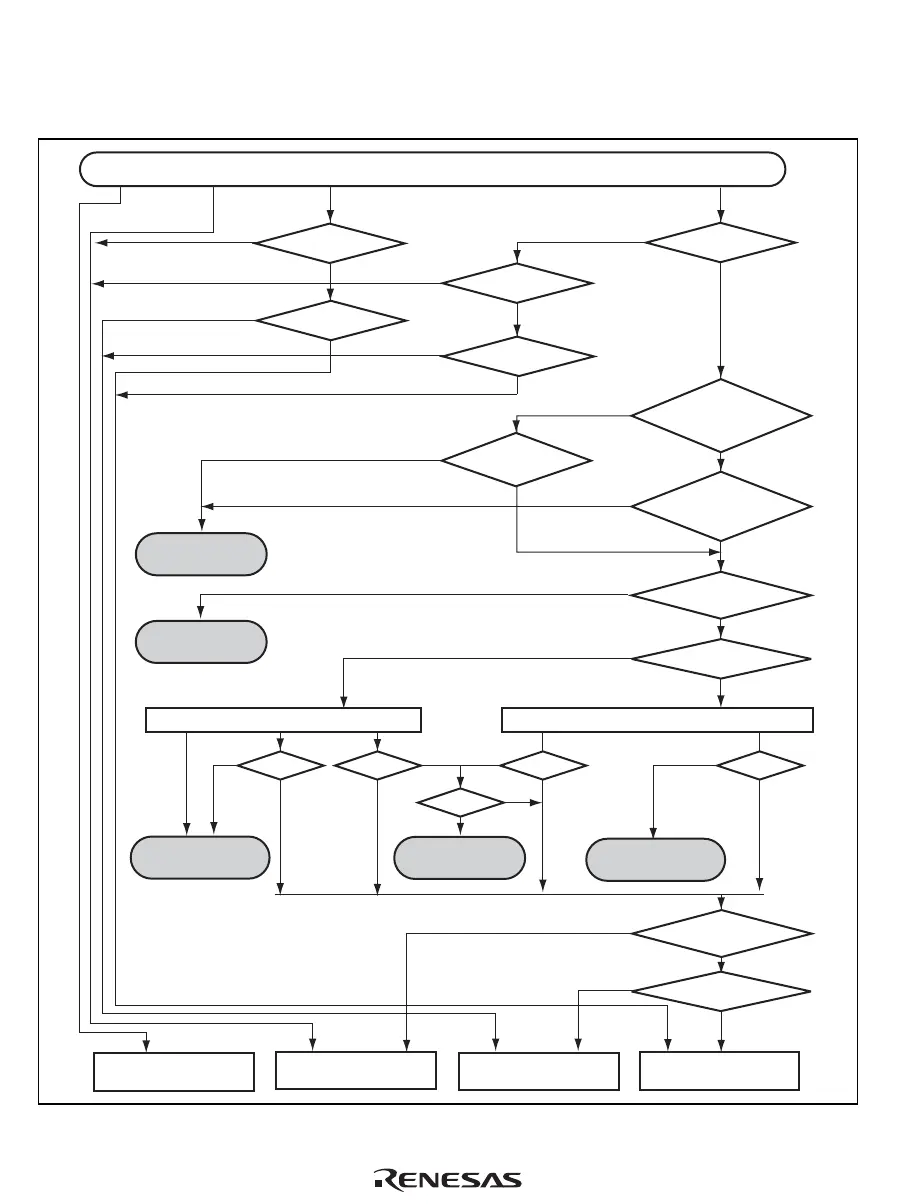

Figure 7.9 shows a flowchart of a memory access using the UTLB.

SR.MD?

R/W?

R/W?

Yes

Yes

No

No

No

Yes

Yes

Yes

No

PR?

PR?

D?

R/W?

WW

W

RRR R

W

R/W?

WT?

1

1

0

0

00 or

01

10

11 01 or 11

00 or 10

Yes

No

Internal resource access

1

0

CCR.OCE?

1

0

CCR.CB?

1

0

CCR.WT?

1

0

CCR.OCE?

No

Data access to virtual address (VA)

VA is

in P4 area

VA is

in P2 area

VA is

in P1 area

VA is in P0, U0,

or P3 area

MMUCR.AT = 1

SH = 0

and (MMUCR.SV = 0 or

SR.MD = 0)

VPNs match,

ASIDs match, and

V = 1

Only one

entry matches

1 (Privileged)

Data TLB multiple

hit exception

Data TLB protection

violation exception

Data TLB miss

exception

0 (User)

VPNs match

and V = 1

Data TLB protection

violation exception

Initial page write

exception

Cache access

in copy-back mode

Cache access

in write-through mode

Memory access

(Non-cacheable)

C = 1 and

CCR.OCE = 1

Figure 7.9 Flowchart of Memory Access Using UTLB

Loading...

Loading...