Rev. 1.50, 10/04, page 68 of 448

5.2.3 Interrupt Event Register (INTEVT)

The interrupt event register (INTEVT) consists of a 14-bit exception code. The exception code is

set automatically by hardware when an exception occurs. INTEVT can also be modified by

software.

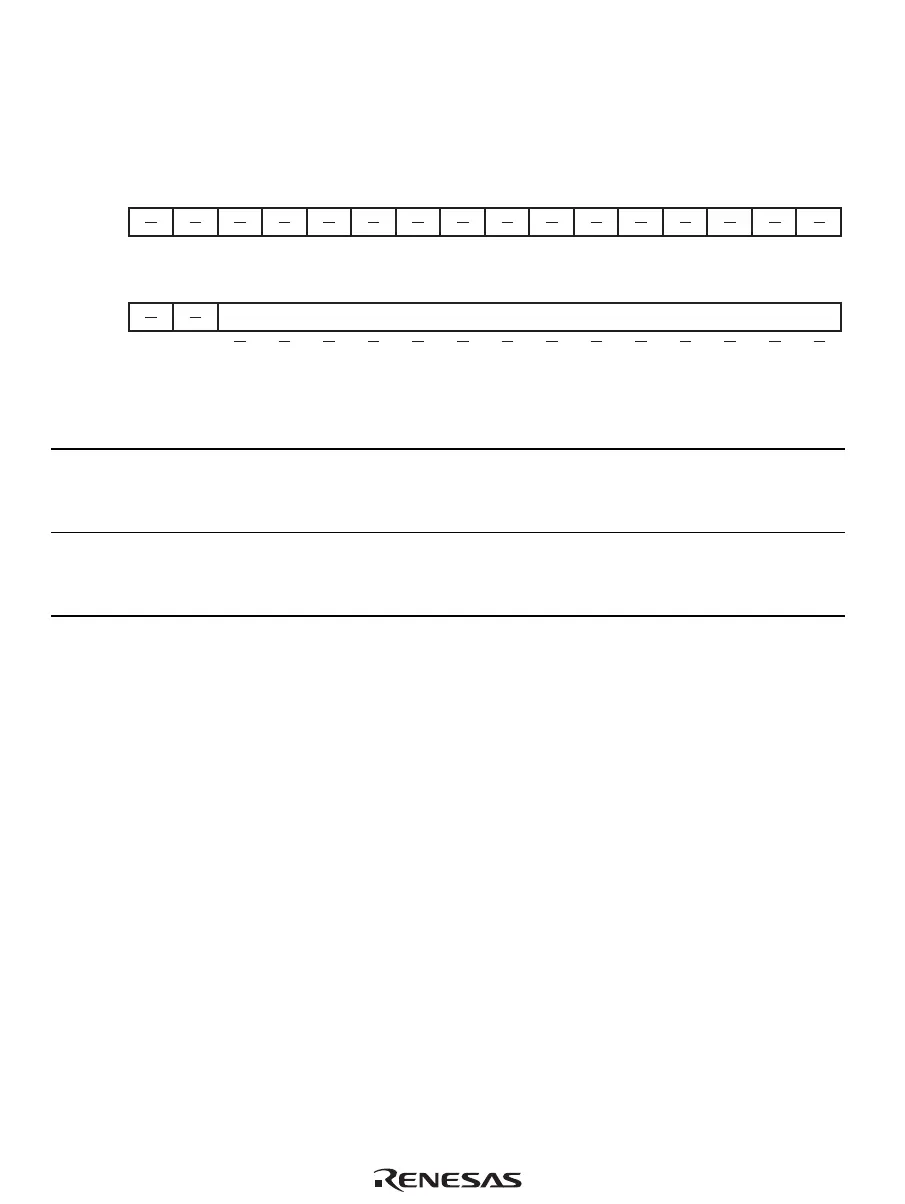

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Bit:

0000000000000000

Initial value:

RRRRRRRRRRRRRRRR

R/W

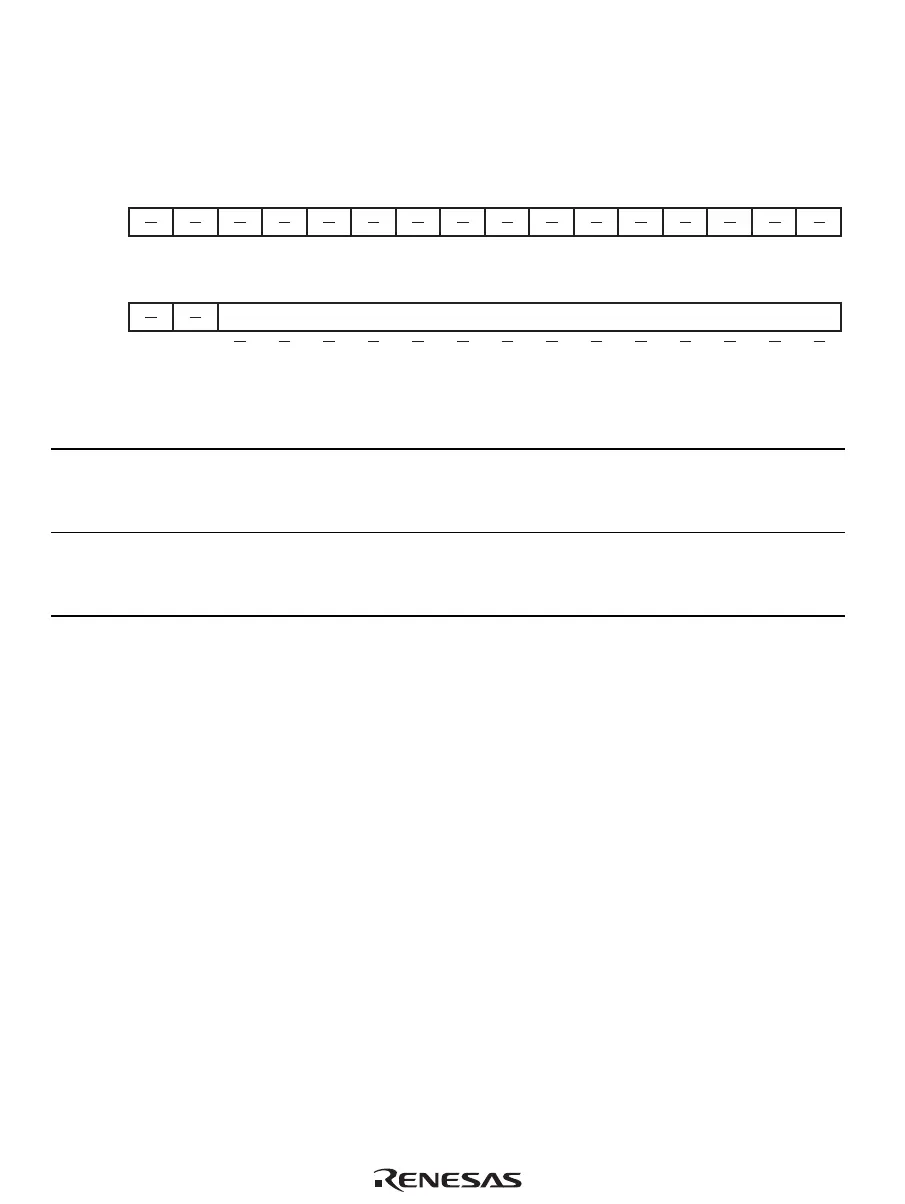

INTCODE

R/W R/W R/W R/W R/W R/W R/W

R/W:

Bit:

Initial value:

R/W:

1514131211109876543210

00

R R R/W R/W R/W R/W R/W

R/W

Bit Bit Name

Initial

Value R/W Description

31 to 14 All 0 R Reserved

For details on reading/writing this bit, see General

Precautions on Handling of Product.

13 to 0 INTCODE Undefined R/W Exception Code

The exception code for an interrupt is set. For details,

see table 5.3.

Loading...

Loading...