Rev. 1.50, 10/04, page 45 of 448

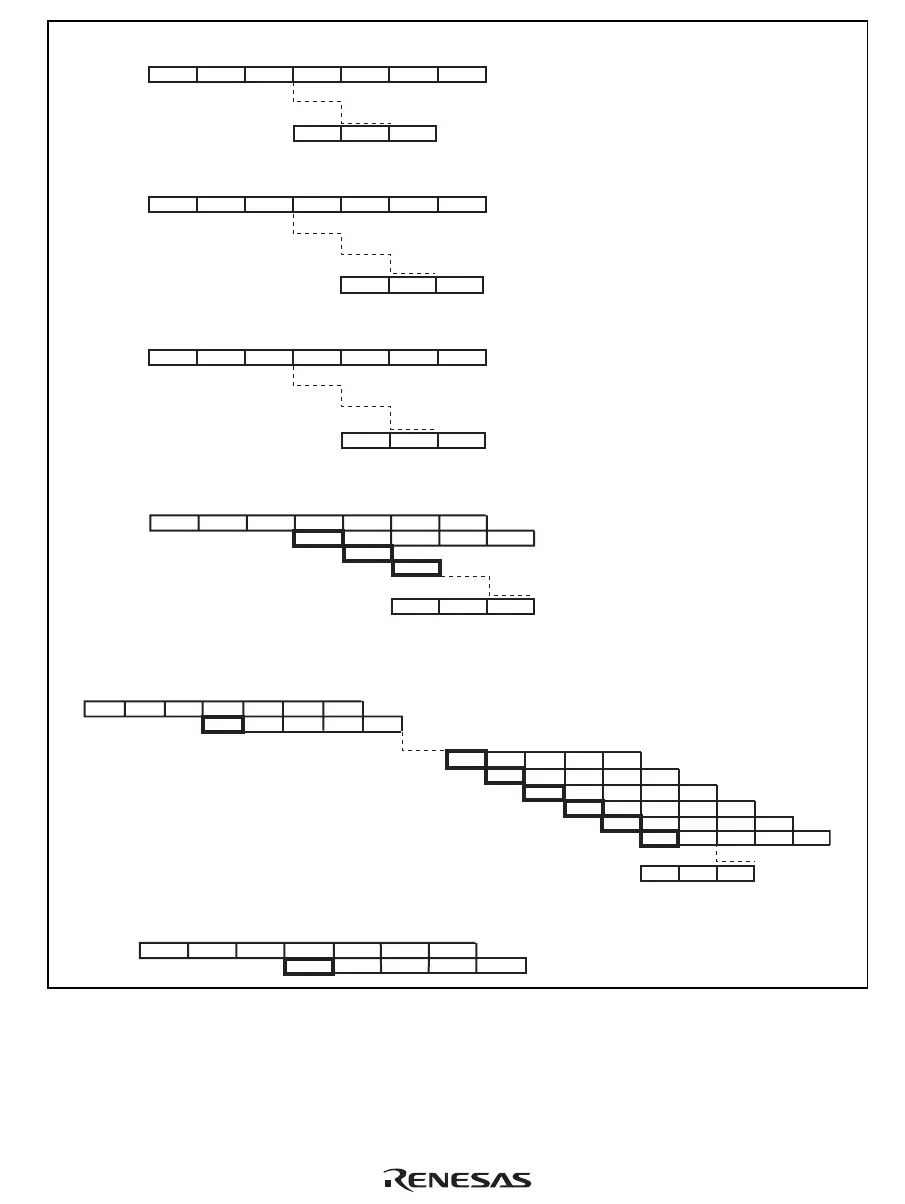

(1-1) BF, BF/S, BT, BT/S, BRA, BSR:

1 issue cycle + 0 to 2 branch cycles

I1 I2

(I1) (ID)

ID E1/S1 E2/s2 E3/s3 WB

(I2)

(1-2) JSR, JMP, BRAF, BSRF:

1 issue cycle + 3 branch cycles

I1 I2 ID E1/S1 E2/S2 E3/S3 WB

(Branch destination instruction)

(1-3) RTS:

1 issue cycle + 0 to 3 branch cycles

I1 I2 ID E1/S1 E2/S2 E3/S3 WB

(1-4) RTE:

4 issue cycles + 1 branch cycles

It is 14 cycles to the ID stage

in the first instruction of exception handler

(1-5) TRAPA: 8

issue cycles + 5 cycles + 1 branch cycle

It is not constant cycles to

the clock halted period.

(1-6) SLEEP: 2

issue cycles

(I1) (ID)(I2)

(Branch destination instruction)

(Branch destination instruction)

(I1) (ID)(I2)

(Branch destination instruction)

In branch instructions that are categorized

as (1-1), the number of branch cycles

may be reduced by prefetching.

Note:

Note:

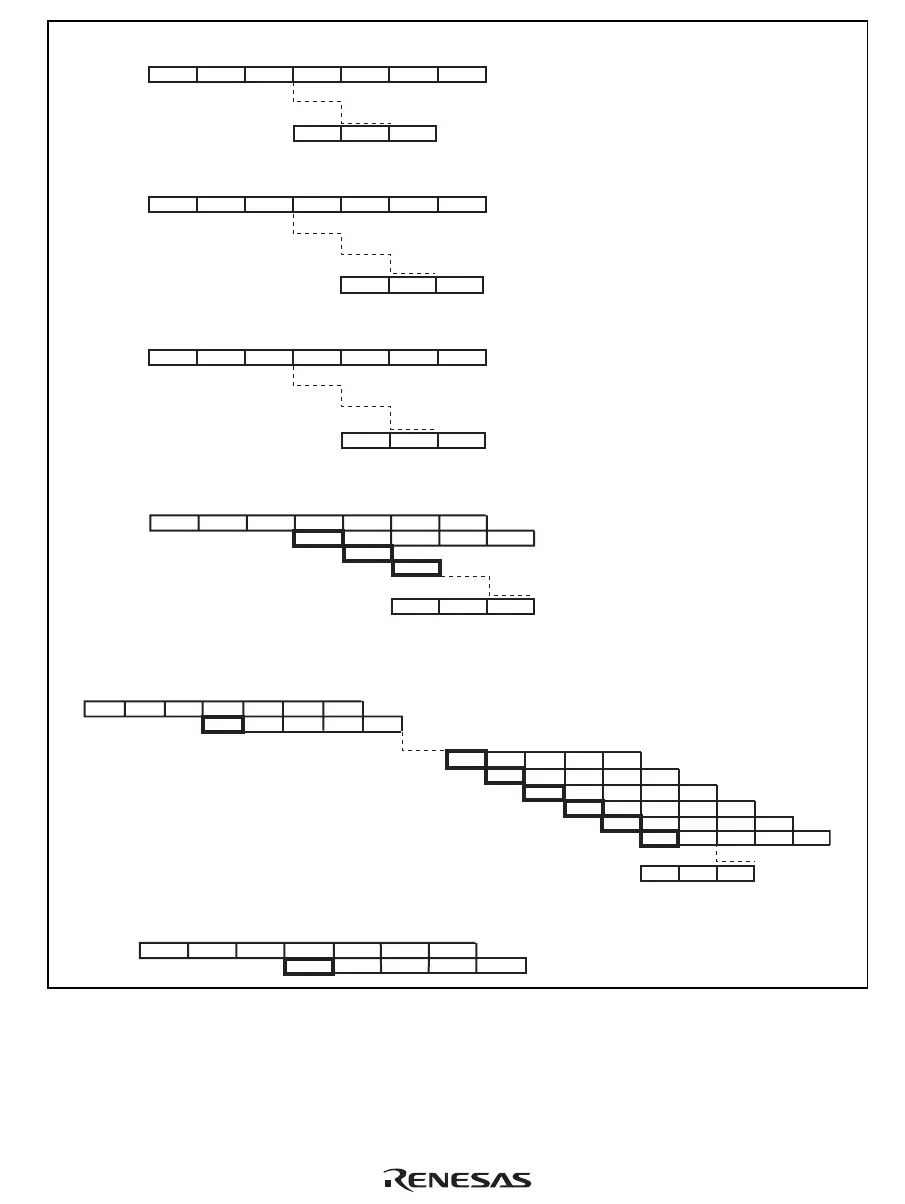

I1 I2 ID s1 s2 s3 WB

E2s2

ID

E3s3

ID

WB

ID

(I1)

(ID)

(I2)

E1s1

I1 I2 ID S1 S2 S3

WB

E1s1

E3s3

E2s2

E1s1

E1s1

E1s1

E1s1

E2s2

E2s2

E2s2

E2s2

E3s3

E3s3

E3s3

E3s3

WB

WB

WB

WB

E2s2 E3s3 WB

E2s2

E3s3

WB

E1s1

E1s1

(I1)

(ID)(I2)

ID

ID

ID

ID

ID

ID

ID

WB

I1 I2 ID S1 S2 S3 WB

E1s1

E2s2

E3s3

WB

ID

Note:

Note: The number of branch cycles may be

0 by prefetching instruction.

Figure 4.2 Instruction Execution Patterns (1)

Loading...

Loading...