Rev. 1.50, 10/04, page 312 of 448

10.1.64 SHLD (Shift Logical Dynamically): Shift Instruction

Format Operation Instruction Code Cycle T Bit

SHLD Rm, Rn When Rm ≥ 0,

Rn << Rm → Rn

When Rm < 0,

Rn >> Rm → [0 → Rn]

0100nnnnmmmm1101 1 —

Description: This instruction logically shifts the contents of general register Rn. General register

Rm specifies the shift direction and the number of bits to be shifted.

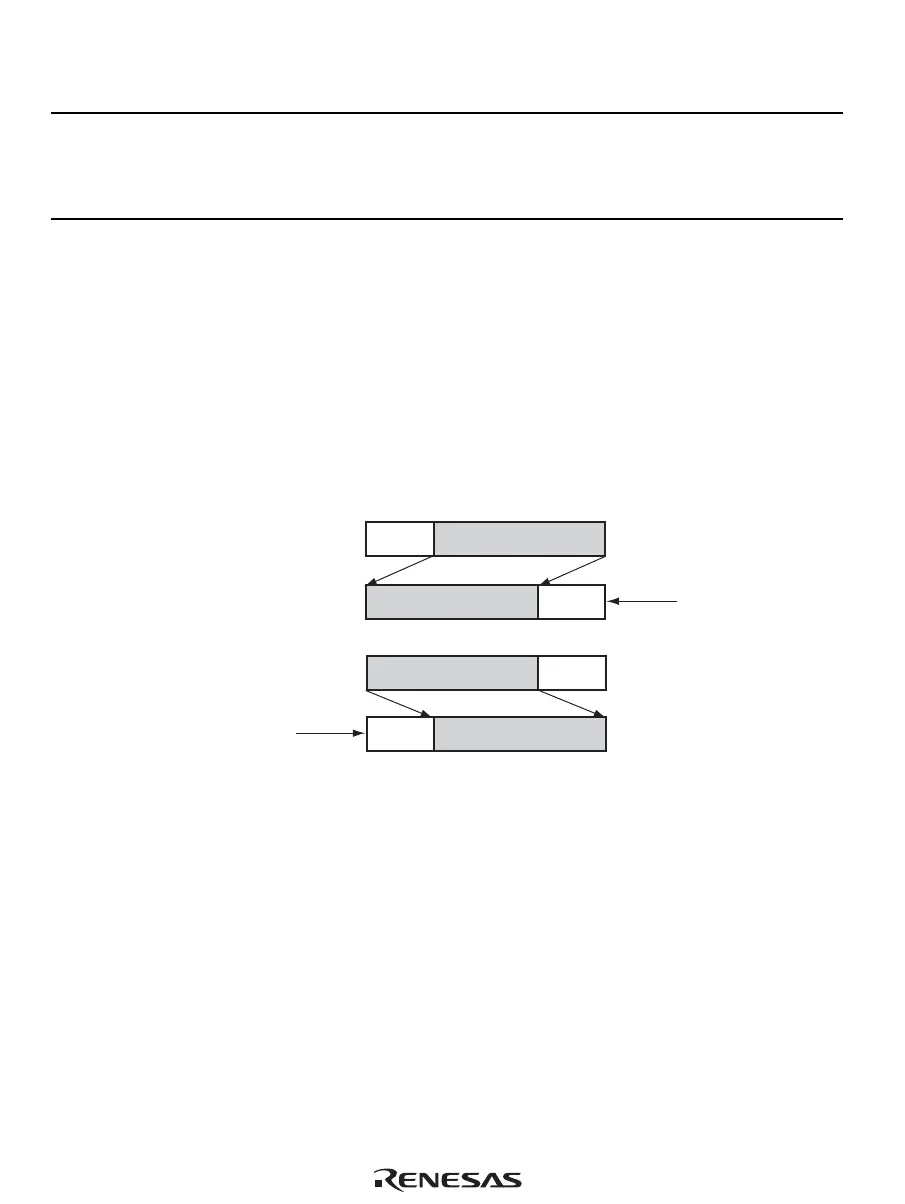

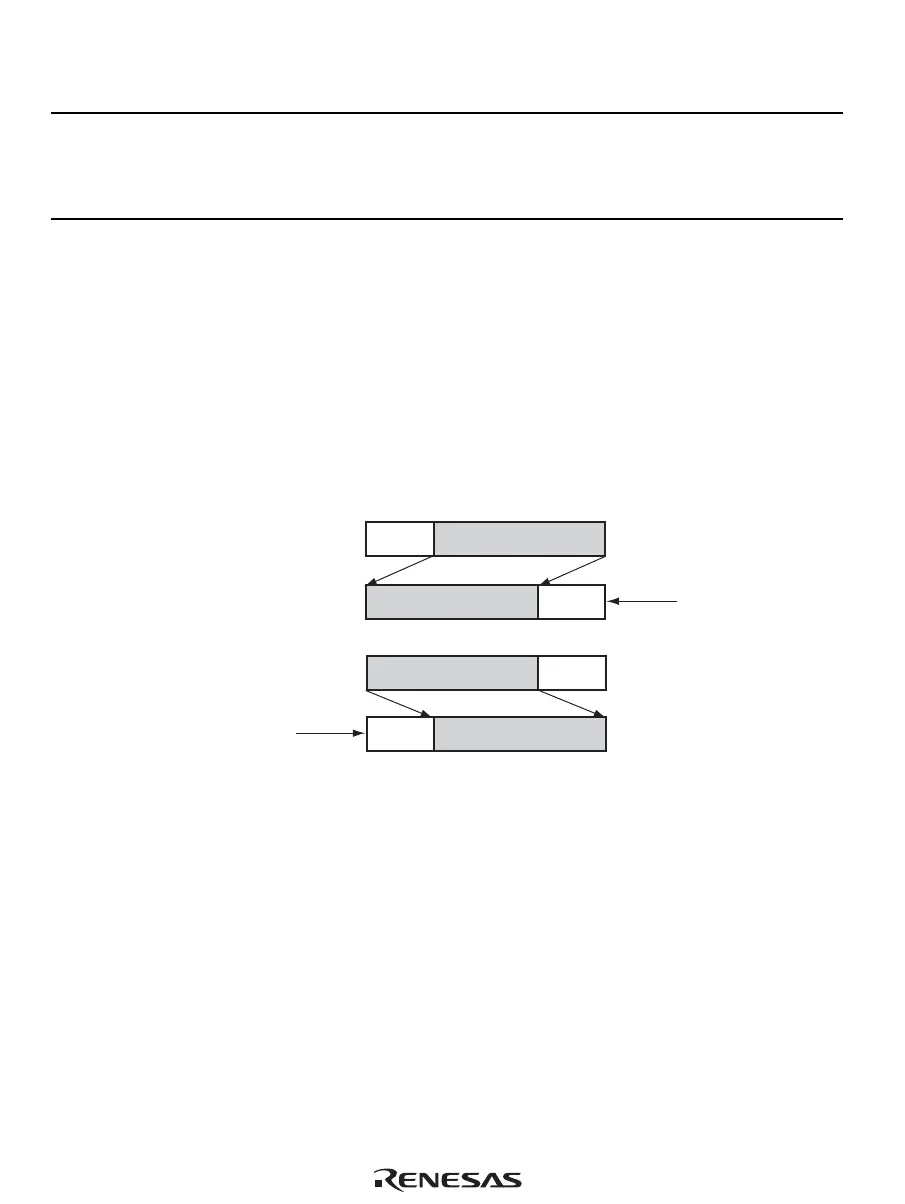

Rn register contents are shifted to the left if the Rm register value is positive, and to the right if

negative. In a shift to the right, 0s are added at the upper end.

The number of bits to be shifted is specified by the lower 5 bits (bits 4 to 0) of the Rm register. If

the value is negative (MSB = 1), the Rm register is represented as a two's complement. The left

shift range is 0 to 31, and the right shift range, 1 to 32.

MSB LSB

MSB

0

LSB

0

Rm ≥ 0

Rm < 0

Notes: None

Loading...

Loading...