Rev. 1.50, 10/04, page 128 of 448

7.2.6 Physical Address Space Control Register (PASCR)

PASCR controls the operation in the physical address space.

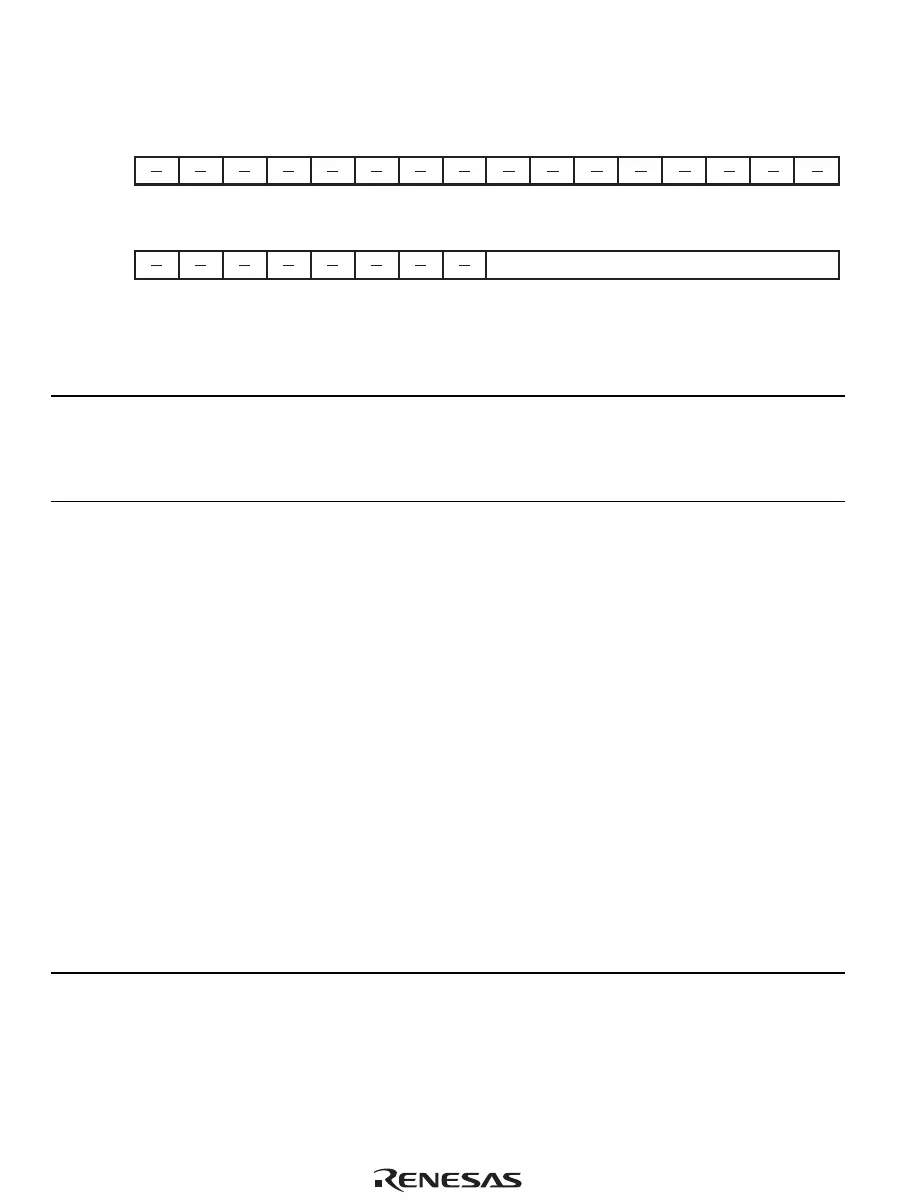

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Bit:

00000000

000000

00000000

Initial value:

RRRRRRRRRRRRRRRR

R/W

UB

R/W R/W R/W R/W R/W R/W R/W

R/W:

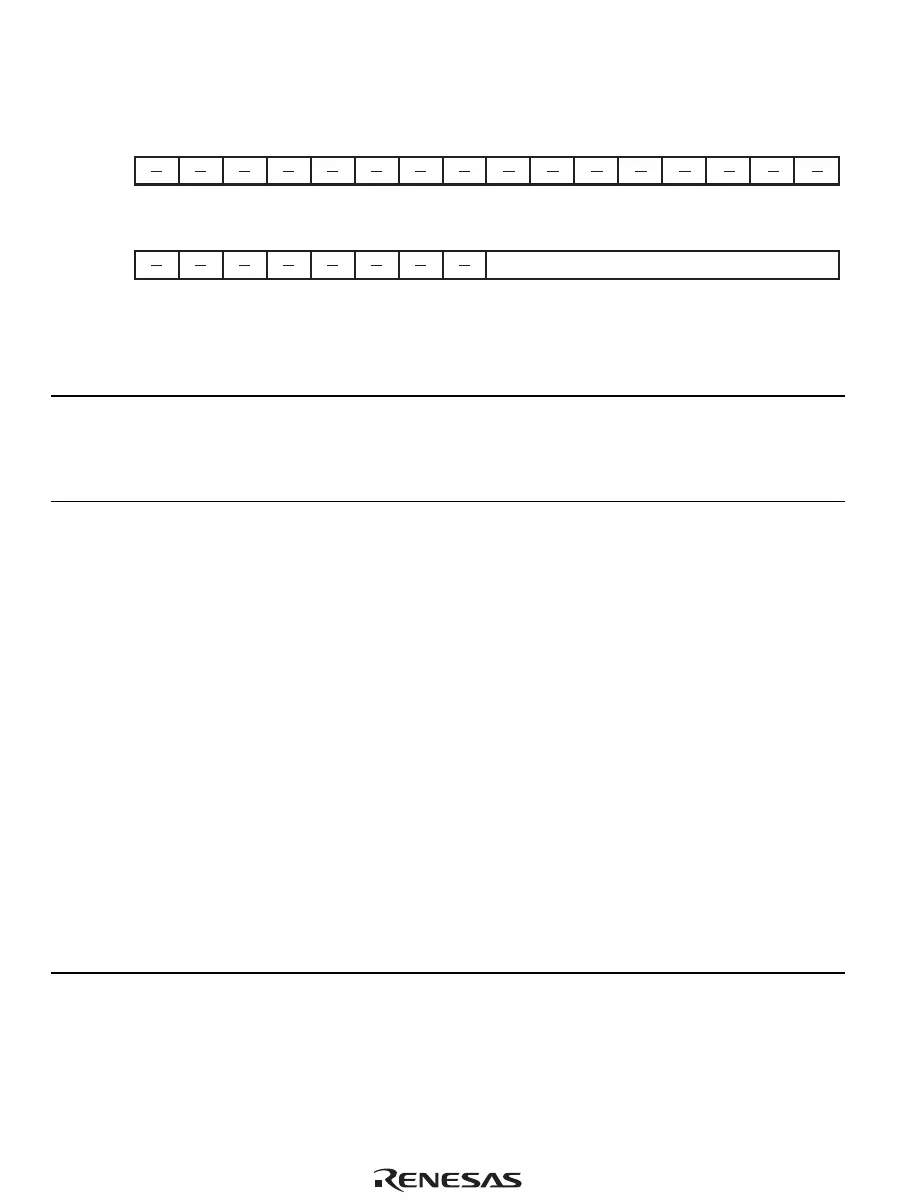

Bit:

Initial value:

R/W:

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

00

000000

00

RRRRRRR

R

Bit Bit Name

Initial

Value R/W Description

31 to 8 All 0 R Reserved

For details on reading from or writing to these bits, see

description in General Precautions on Handling of

Product.

7 to 0 UB All 0 R/W Buffered Write Control for Each Area (64 Mbytes)

When writing is performed without using the cache or in

the cache write-through mode, these bits specify

whether the next bus access from the CPU waits for the

end of writing for each area.

0 : The CPU does not wait for the end of writing bus

access and starts the next bus access

1 : The CPU waits for the end of writing bus access and

starts the next bus access

UB[7]: Corresponding to the control register area

UB[6]: Corresponding to area 6

UB[5]: Corresponding to area 5

UB[4]: Corresponding to area 4

UB[3]: Corresponding to area 3

UB[2]: Corresponding to area 2

UB[1]: Corresponding to area 1

UB[0]: Corresponding to area 0

Loading...

Loading...