123

1

22

20

27

26

2

23

21

24

25

3

4

5

6

7

8

9

10

14

28

19

18

17

16

15

13

12

11

22

20

27

26

2

23

21

24

25

3

4

5

6

7

8

9

10

14

28

19

18

17

16

15

13

12

11

6

3

4

5

1

10

1

7

1

10

1

4

1

3

1

9

1

4

1

2

1

5

1

3

1

4

5

1

2

1

9

1

8

1

7

1

6

1

6

1

7

1

2

110

18

16

14

12

1

2

4

6

8

9

7

5

3

19

11

13

15

17

8

10

9

6

4

5

3

1

2

11

13

12

37 1 13 36 68 14 12

2

6

5

7

4

11

10

8

9

43

64

67

65

16

3

63

62

61

40

41

28

29

34

35

66

19

20

21

22

23

30

31

32

18

17

15

44

42

39

33

38

24

25

26

27

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

1

23456789

10

1

98765432

10

19

18

17

16

15

14

13

12

1

11

2

3

4

5

6

7

8

9

19

18

17

16

15

14

13

12

1

11

2

3

4

5

6

7

8

9

11

12

13

3

1

2

6

4

5

8

9

10

13

4

1

2

3

14

15

5

12

9

10

11

6

7

2

3

7

1

58

4

6

1011

89

4365

211213

8

9

10

11

12

1

2

13

4

5

6

7

2

3

1

12

11

10

9

14

13

15

18

17

16

15

14

13

12

11

1

19

2

3

4

5

6

7

8

9

18

17

16

15

14

13

12

11

1

19

2

3

4

5

6

7

8

9

3

5

7

9

11

13

1

2

4

6

10

15

12

14

5

6

7

11

10

9

4

3

2

1

15

14

13

12

1

3

A16

A6

A18

A11

C11

C15

A14

C14

A15

C25

A25

C24

A24

A28

A27

C27

A26

A31

A8

C9

C8

C31

C12

8

16

7

14

7

14

816

7

816

20

10

816

1020

7

14

1020

10

10

20

20

J1

U14

U15

U6

C16

C5

C7

C9

C12

C2

C6

C3

C1

C10

C13

C17

C11

RZ2

RZ1RZ1

RZ6RZ6

RZ1RZ1

RZ6

RZ6

RZ2RZ2

RZ2

RZ2

RZ2RZ2RZ2RZ2

RZ6

RZ6

RZ1

U1

U1

U3

U3

U3

U3

R6

R11

R3

R2

R7

R4

R8

U9

RZ3

RZ4

U13

U12

U10

U10

U10

U10

U7

U7

TP6

TP3

TP4

TP1

TP2

R10

R1

R9

R5

R26

TP5

U8

U2

U2

U2U2

U2

U2

U6

U6

U11

U11

U16

U17

Y1

U5

U4

C24

C25

C26

C8

C15

C27

C14

C4

S1

ALARM-X

7. ALL CAPACITORS ARE .1uF/50V. UNLESS OTHERWISE SPECIFIE

BA

B - 27C256

A - 27C64/27C128

GENERATED BY HSO PERIPHERAL

N.O.

SUPERVISOR

3. EXTERNAL 2KHZ CLOCK RECEIVED FROM

ON THE INTERNAL I/O DATA BUS

3. READY - LOGIC 0 RESULTS IN PROGRAMMED NUMBER OF WAIT STATES

2. BUSWIDTH - LOGIC 1 = 16 BIT BUS WIDTH

6. TEST PROGRAM SIGNAL - IF THE INPUT TO THIS PIN IS A LOGIC 1

5. AN INTERNALLY GENERATED 2KHZ/1.667KHZ CLOCK SIGNAL WILL BE PRESENT

DYNAMIC SELECTION OF THE BUS WIDTH, ONE WAIT STATE FOR

EXTERNAL I/O CYCLES, ADV SIGNAL ON PIN 62, AND /WR ON PIN 41

4. THE CHIP CONFIGURATION REGISTER IS PROGRAMMED TO ALLOW

LOGIC 0 = 8 BIT BUS CYCLE

P1.3 CCT-U (TRIP ENABLED)

P1.2 BACK UP ENABLED

P1.1 ALARM

TN80C196KC-16 SIGNALS -

5. COMMUNICATIONS INTERRUPT REQUEST

4. INTERNAL I/O BUS ACTIVE = LOGIC 0

6. MICROCONTROLLER CLOCK - 8MHZ

ONE-SHOT PULSE WIDTH: Tw = RC

2. SYSTEM 2KHZ/1.667KHZ CLOCK

1. WATCHDOG TIMER PULSES

TEST POINTS:

BINARY CODE ON THE CARD ID #1 & CARD ID#2 PINS

THE PROCESSOR WILL RUN A TEST PROGRAM DETERMINED BY THE

ON TEST POINT 2

1.

NOTES:

JUMPER:

+5

WR

CS

RD

AUX-CT DATA

INPUT DATA

AUX-CT CONTROL

OUTPUT DATA

INTERNAL I/O

L 3A EN OUT

A/D CHIP SEL

WRITE DATA EN

PWR UP RESET

DC RESTORE

R1.5A EN1

R1.5A EN2

R3A EN IN

LCCT ALARM IN

A 3PT

BACK-UP EN

INT-X

SUP EN

50HZ60/

LCCT ALARM OUT

(8001)

(8001)

(8000)

(8000)

FROM SHEET 2)

(INTERNAL I/O

D7

D6

D5

D4

D3

D2

D1

D0

CARD ID#1

CARD ID#2

TEST PROGRAM

A/D CLOCK

OUTPUT LATCH EN

CLOCKSYSTEM

ALARM 3

ALARM 2

ALARM 1

+5

+5

+5

+5

+5

+5

+5

+5

+5

+5

+5

+5

+5

+5

+5

+5

+5

+5

+5

+5

+5

+5

+5

+5

+5

+5

+5

+5

+5

(TO SHEET 2)

DATA BUS

DATA BUS

D7

D6

D5

D4

D3

D2

D1

D0

+5

+5

+5

+5+5

27HC64

27HC64

HC10

HC240

HC240

HC125

HC125

HC125

HC125

TN80C196KC-16

HC573

HC573

HC00

HC00

HC00

HC00

HC123

HC123

HC05

HC05

HC05HC05

HC05

HC05

HC10

HC10

HC139

HC139

HC541

HC541

HC367

HC251

O0

O1

O2

O3

O4

O5

O6

O7

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

CE

OE

VPP

O0

O1

O2

O3

O4

O5

O6

O7

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

CE

OE

VPP

10K

10K

10K

10K

10K

10K

10K

10K

10K

10K

10K

A1

A2

A3

A4

Y1

Y2

Y3

Y4

G

A1

A2

A3

A4

Y1

Y2

Y3

Y4

G

1K

10K

1K

1K

10K

1K

10K

EA

BUSWIDTH

READY

HSI.3/HS0.5

HSI.2/HS0.4

HSI.1

HSI.0

T2CAPT/P2.7

T2UP-DN/P2.6

PWMO/P2.5

T2RST/P2.4

T2CLK/P2.3

EXTINT/P2.2

RXD/P2.1

TXD/P2.0

XTAL2

XTAL1

HS0.3

HS0.2

HS0.1

HS0.0

WRH/BHE

DF

G

N

A

S

S

S

S

S

S

E

R

C

C

P

P

VVV VVV

WRL/WR

RD

ALE/ADV

INST

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

AD8

AD9

AD10

AD11

AD12

AD13

AD14

AD15

HOLD/P1.7

HLDA/P1.6

BREQ/P1.5

PWM2/P1.4

PWM1/P1.3

P0.7

P0.6

P0.5

P0.4

P0.3

P0.2

P0.1

P0.0

P1.2

P1.1

P1.0

NMI

RESET

CLKOUT

10K

10K

OC

C

1D

2D

3D

4D

5D

6D

7D

8D 8Q

7Q

6Q

5Q

4Q

3Q

2Q

1Q

OC

C

1D

2D

3D

4D

5D

6D

7D

8D 8Q

7Q

6Q

5Q

4Q

3Q

2Q

1Q

Q

Q

REXT

CEXT

CLR

B

A

Q

Q

REXT

CEXT

CLR

B

A

154K

1K

5.62K

1K

10K

RESET

VOUT

PFO

VBATT

PFI

WDI

VCC

GND

EN

B

A

Y3

Y2

Y1

Y0

EN

B

A

Y3

Y2

Y1

Y0

A5

A3

A4

A6

A7

A8

Y1

Y2

Y3

Y4

Y5

Y6

Y7

Y8

A1

A2

G1

G2

A5

A3

A4

A6

A7

A8

Y1

Y2

Y3

Y4

Y5

Y6

Y7

Y8

A1

A2

G1

G2

16MHZ

1Y1

1Y2

1Y3

1Y4

2Y1

2Y2

1G

2G

1A1

1A2

1A3

1A4

2A1

2A2

D7

D6

D5

D4

D3

D2

D1

D0

SELC

SELB

SELA

STRB

W

Y

.01uf

.01uf

22pf22pf

P1

P1

P1

P1

P1

P1

P1

P1

P1

P1

P1

P1

P1

P1

P1

P1

P1

P1

P1

P1

P1

P1

P1

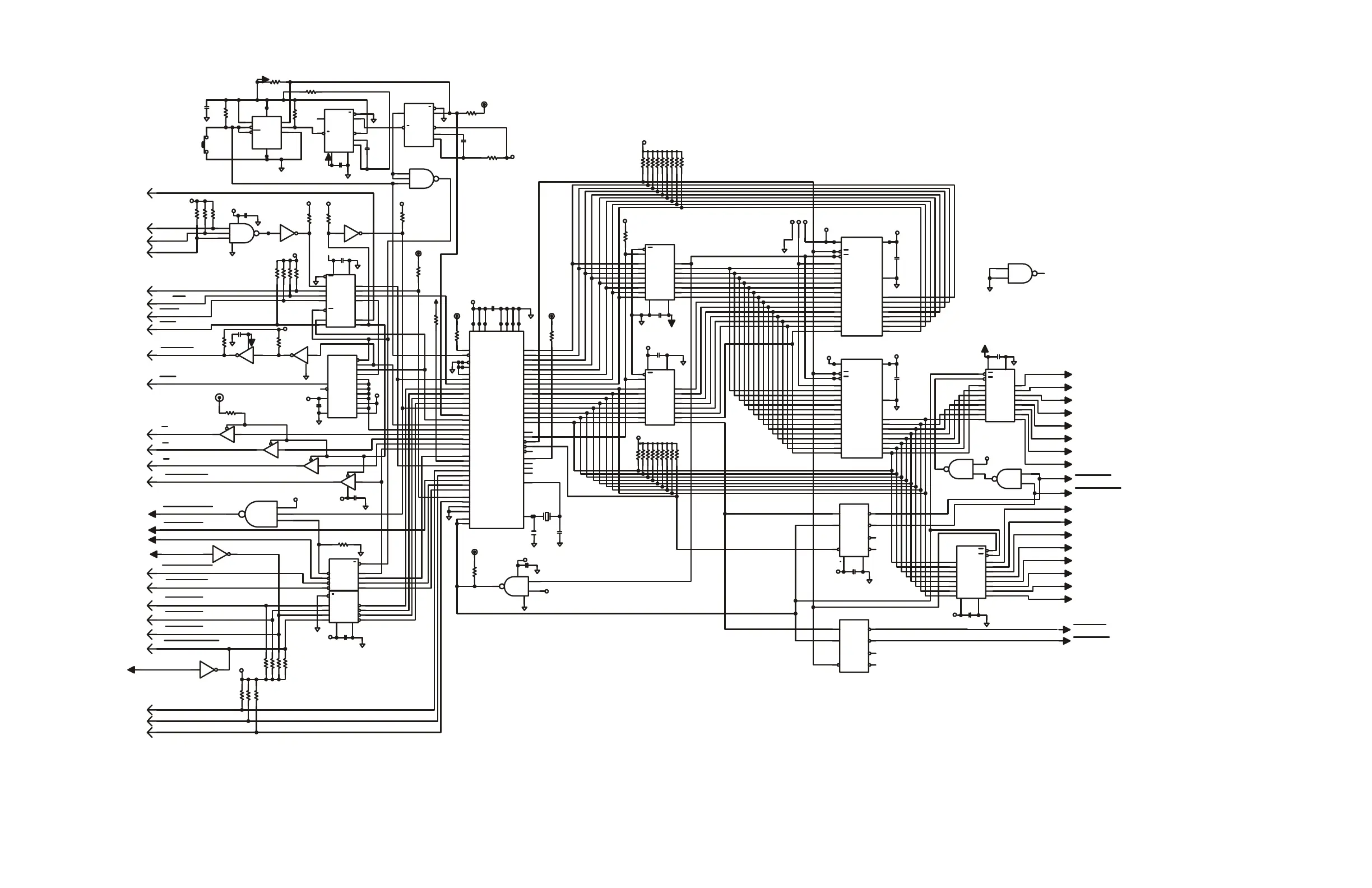

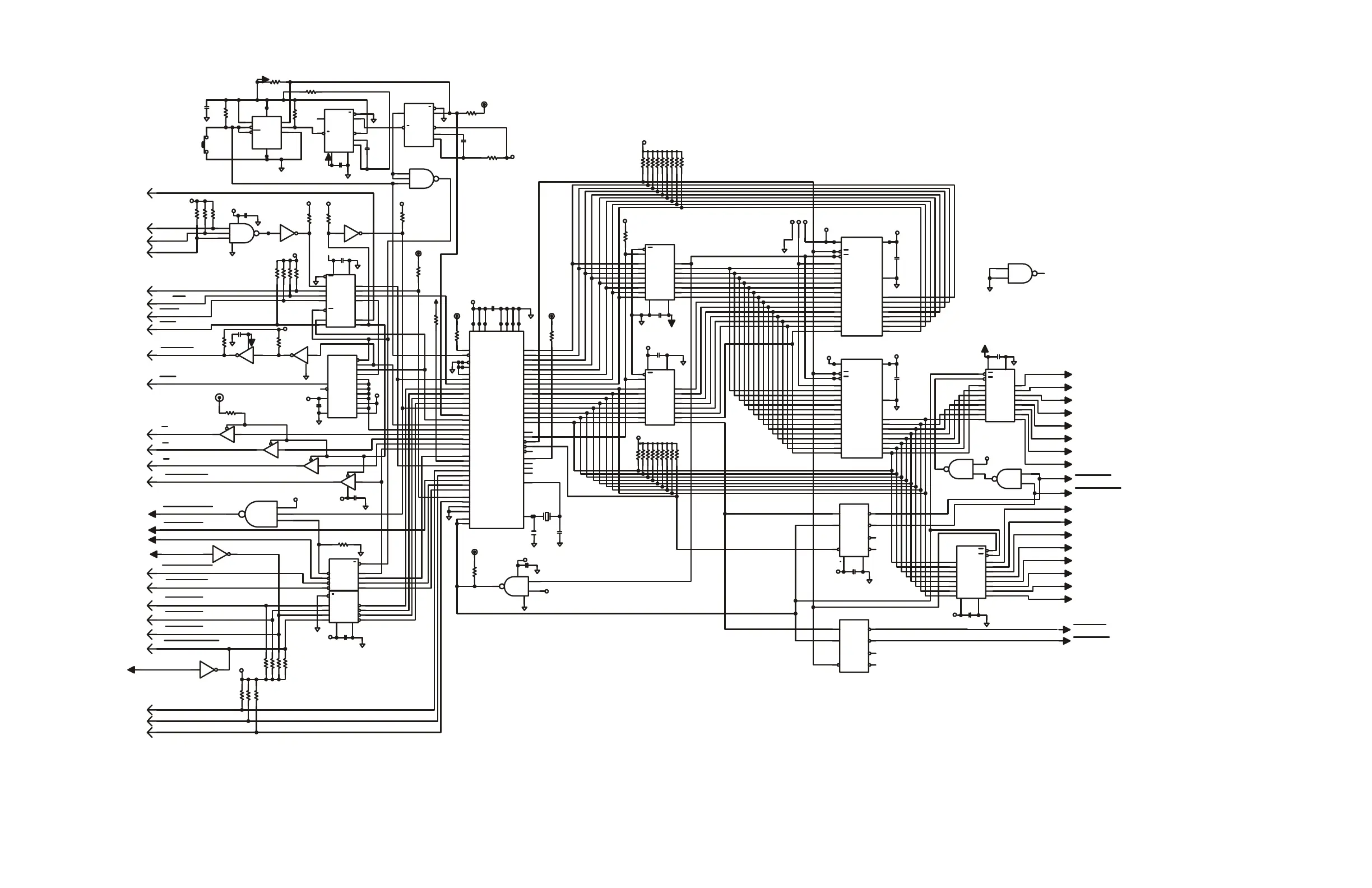

Figure 12- 4. Phase Controller modules for

RFL 9300 Charge Comparison System

(Assembly No. 106370; Schematic No. D-103819, Rev. D)

Sheet 1 of 2

RFL 9300 RFL Electronics Inc.

September 10, 2007 32 -9 (973) 334-3100

Loading...

Loading...