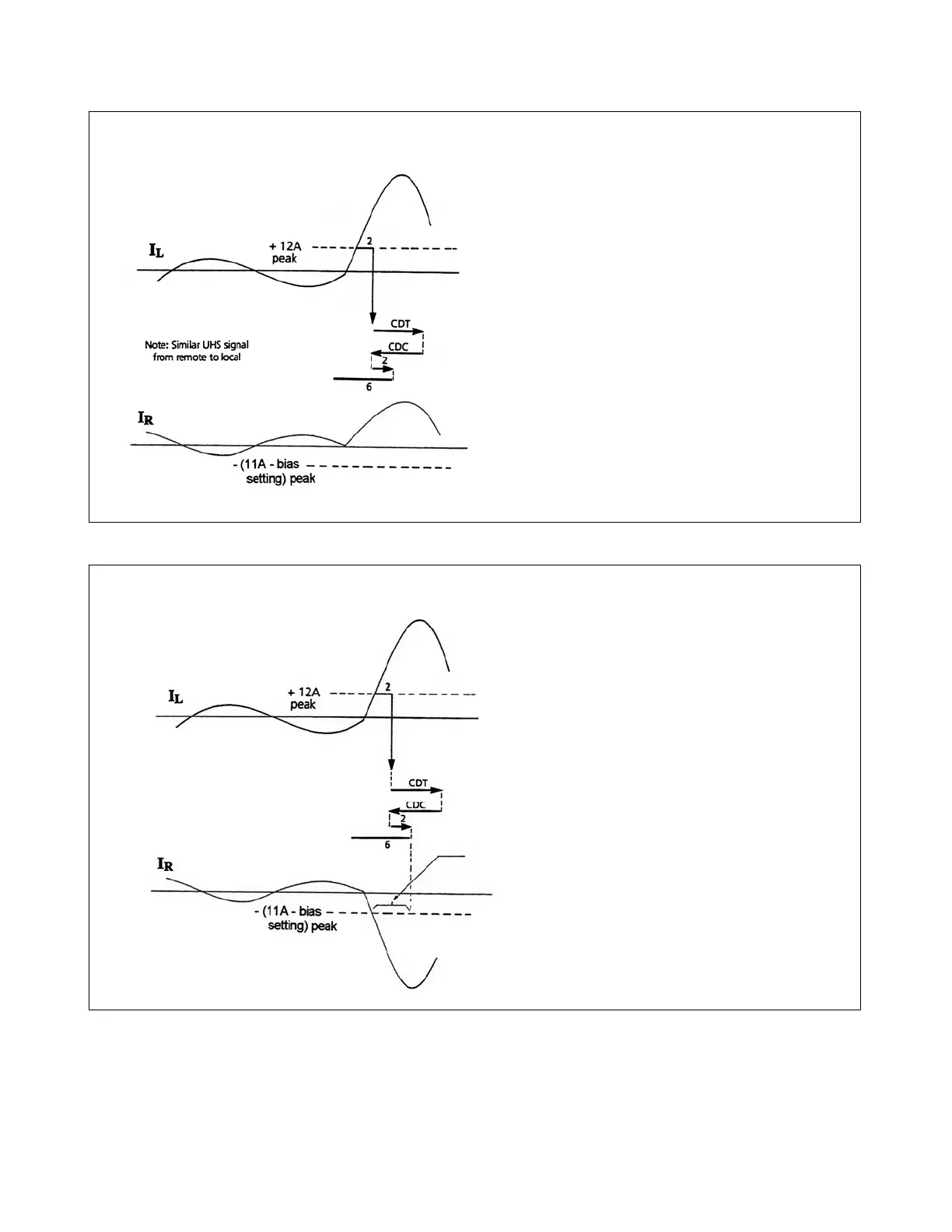

Figure 3- 11. Operation of the RFL 9300’s UHS circuit during an internal fault

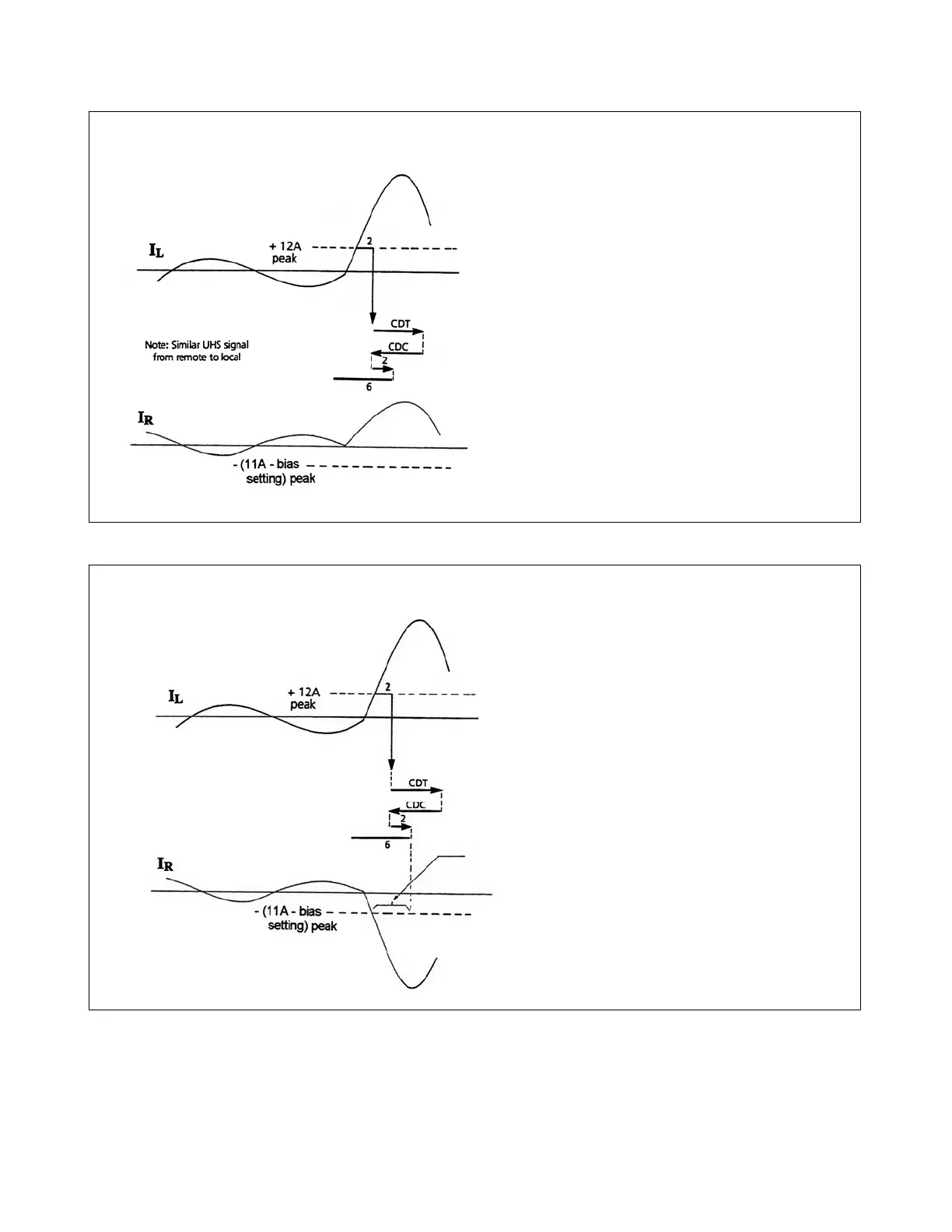

Figure 3-12. Operation of the RFL 9300’s UHS circuit during and external fault

Correct blocking during this time interval.

(Only 1 sample equal to – (11A – bias

setting) peak, or more negative, is re-

quired to block UHS tripping)

2: 2ms dwell time at +12A peak. (Create UHS)

CDT: Channel Delay Time

CDC: Channel Delay Compensation

2: “Reach Forward Time” of 2 ms

6: Time window of 6 ms that looks for – (11A –

bias setting) peak sample to block UHS.

RFL 9300 RFL Electronics Inc.

August 25, 2000 3 - 10 (973) 334-3100

Loading...

Loading...