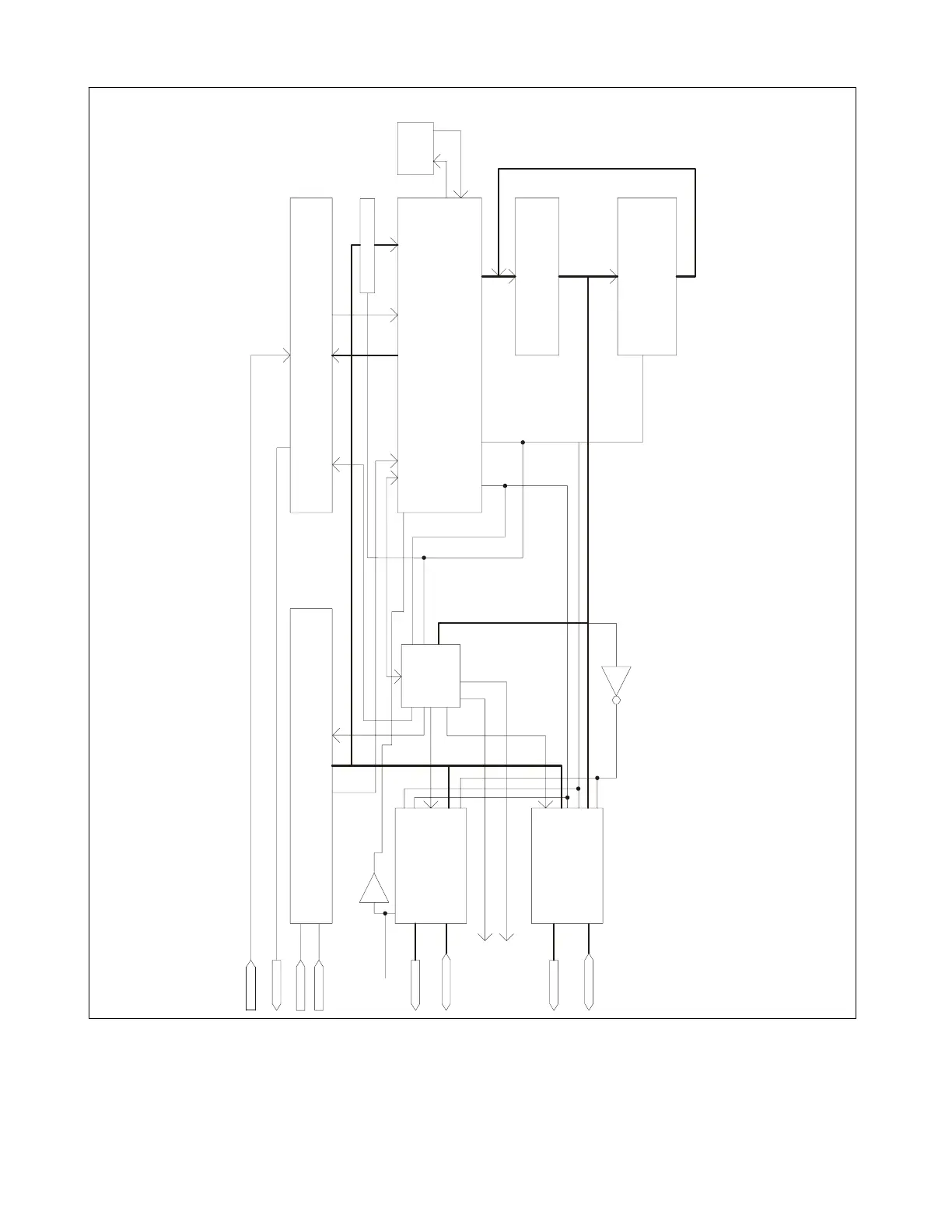

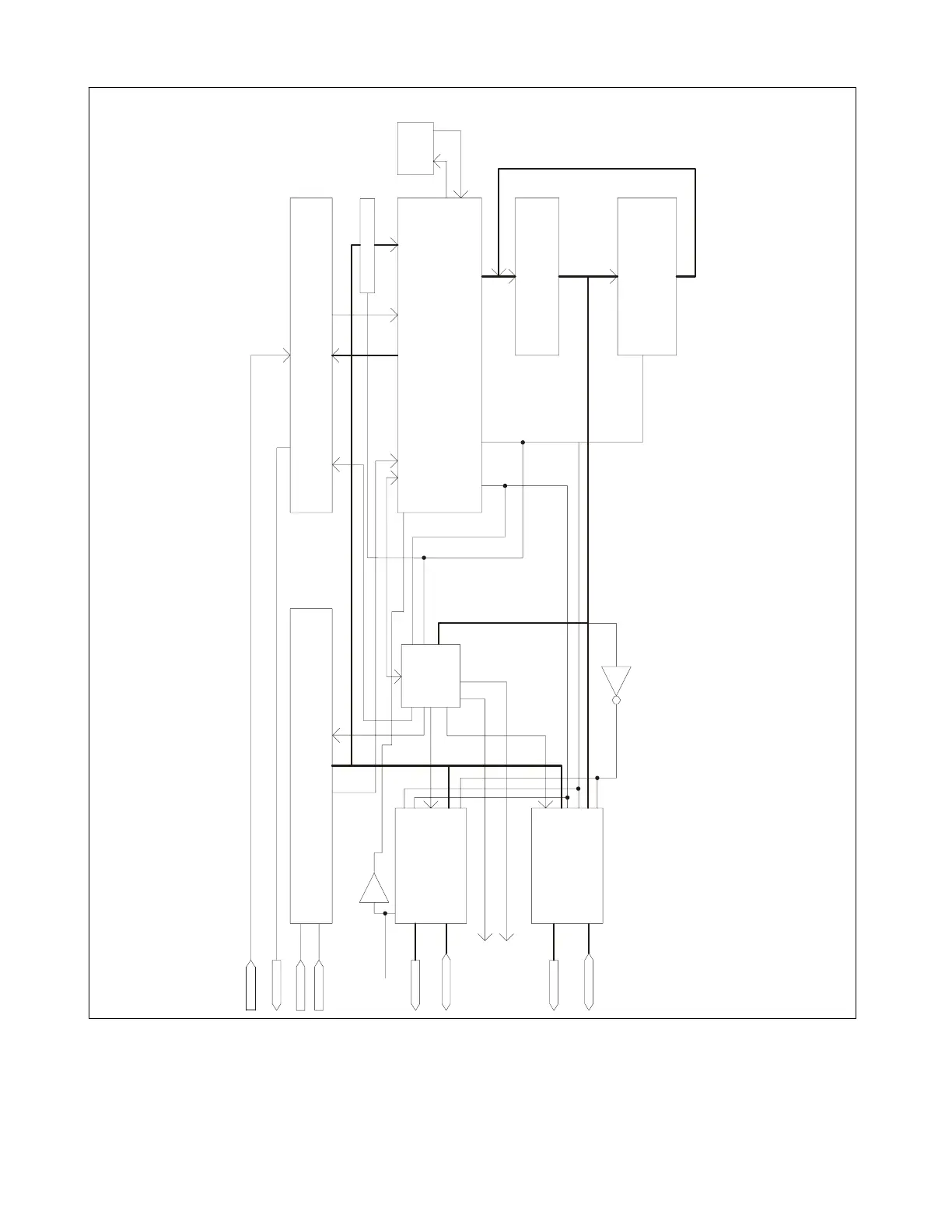

SERIAL RECEIVER

U3, U4, U5, U6, U1, U8, U9

U7

U13, U14, U12, U15, U16

SERIAL TRANSMITTER

80C196KC

MICROCONTROLLER

LATCH

U17

SUPERVISOR

I/O BUS

U27, U28

MODEM

BUS I/O

ADDRESS

DECODER

U24

ADDRESS LATCH

U19, U20

RESIDENT PROGRAM

MEMORY

U21, U28

EXTERNAL I/O BUS

WATCH

DOG

U30

/RESET

READ BUS

PORT 0

BUS INBUS OUT

TX INTERRUPT

MUX CPU BUS

/READ STROBE

/WRITE STROBE

/RD/WR

SUP SELECT

/RD

/WR

/MODEM SELECT

STANDBY

ALARM

A15, A9

A16

A15-A8

A15-A8

BUS DIRECTION

CONTROL LINE

(OUT IF HIGH)

ADDRESS LINE A15

LATCHED

ADDRESS

ADDRE

ED PR

RAM

DE

WAIT STATE

RX INTERRUPT

/RX STROBE

TX /MSB & LSB STROBE LINES

FRM 93_SV

/COM EN

TX CLOCK

TX DATA

RX DATA

RX CLOCK

93_SV

MODEM

93_SV

MODEM

U26

U25

U27

U28

Figure 13-3. Block diagram, RFL 9300 communications controller module

RFL 9300 RFL Electronics Inc.

February 7, 2000 13 - 4 (973) 334-3100

Loading...

Loading...