18.19

Date Code 20171006 Instruction Manual SEL-400 Series Relays

Synchrophasors

Synchrophasor Quantities

When using the relay as a synchrophasor client, the Relay Word bits in Table 18.9

indicate the state of the synchronization.

When received, synchrophasor messages contain digital data. These data are

stored in the Remote Synchrophasor Relay Word bits in Table 18.10.

Analog Quantities

The synchrophasor measurements in Table 18.11 are available whenever Global

setting EPMU := Y. When EPMU := N, these analog quantities are set to 0.0000.

It is important to note that the synchrophasors are only valid when the relay is in

HIRIG or HPTP timekeeping mode, which can be verified by monitoring the

TSOK Relay Word bit. When TSOK = logical 1, the relay timekeeping is syn-

chronized to the high-accuracy IRIG-B signal or PTP time source, and the syn-

chrophasor data are precisely time-stamped.

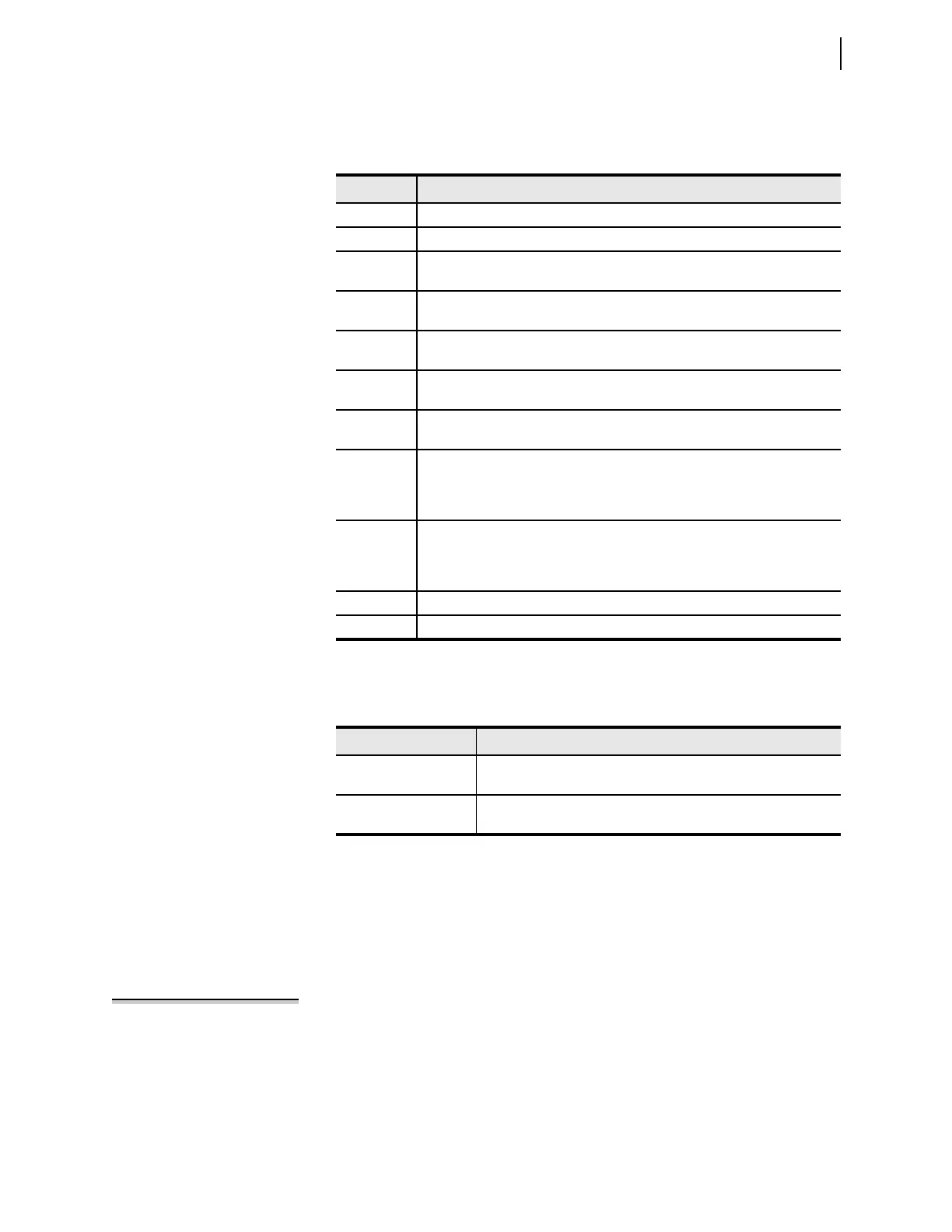

Table 18.9 Synchrophasor Client Status Bits for Real-Time Control

Name Description

RTCENA Asserts for one processing interval when a valid message is received on Channel A.

RTCENB Asserts for one processing interval when a valid message is received on Channel B.

RTCROKA Asserts for one processing interval when data are aligned for Channel A. Use

this bit to condition usage of the Channel A data.

RTCROKB Asserts for one processing interval when data are aligned for Channel B. Use

this bit to condition usage of the Channel B data.

RTCROK Asserts for one processing interval when data for all enabled channels are

aligned. Use this bit to condition general usage of the aligned synchrophasor data.

RTCDLYA This bit is asserted when the last received valid message on Channel A is older

than MRTCDLY.

RTCDLYB This bit is asserted when the last received valid message on Channel B is older

than MRTCDLY.

RTCSEQA This bit is asserted when the processed received message on Channel A is the

expected next-in-sequence. It is deasserted if it is not. The deassertion implies

that one or more packets of information were lost. Use this bit to condition

usage of channel A data in applications where sequential data are required.

RTCSEQB This bit is asserted when the processed received message on Channel B is the

expected next-in-sequence. It is deasserted if it is not. The deassertion implies

that one or more packets of information were lost. Use this bit to condition

usage of channel B data in applications where sequential data are required.

RTCCFGA Indicates Channel A is successfully configured.

RTCCFGB Indicates Channel B is successfully configured.

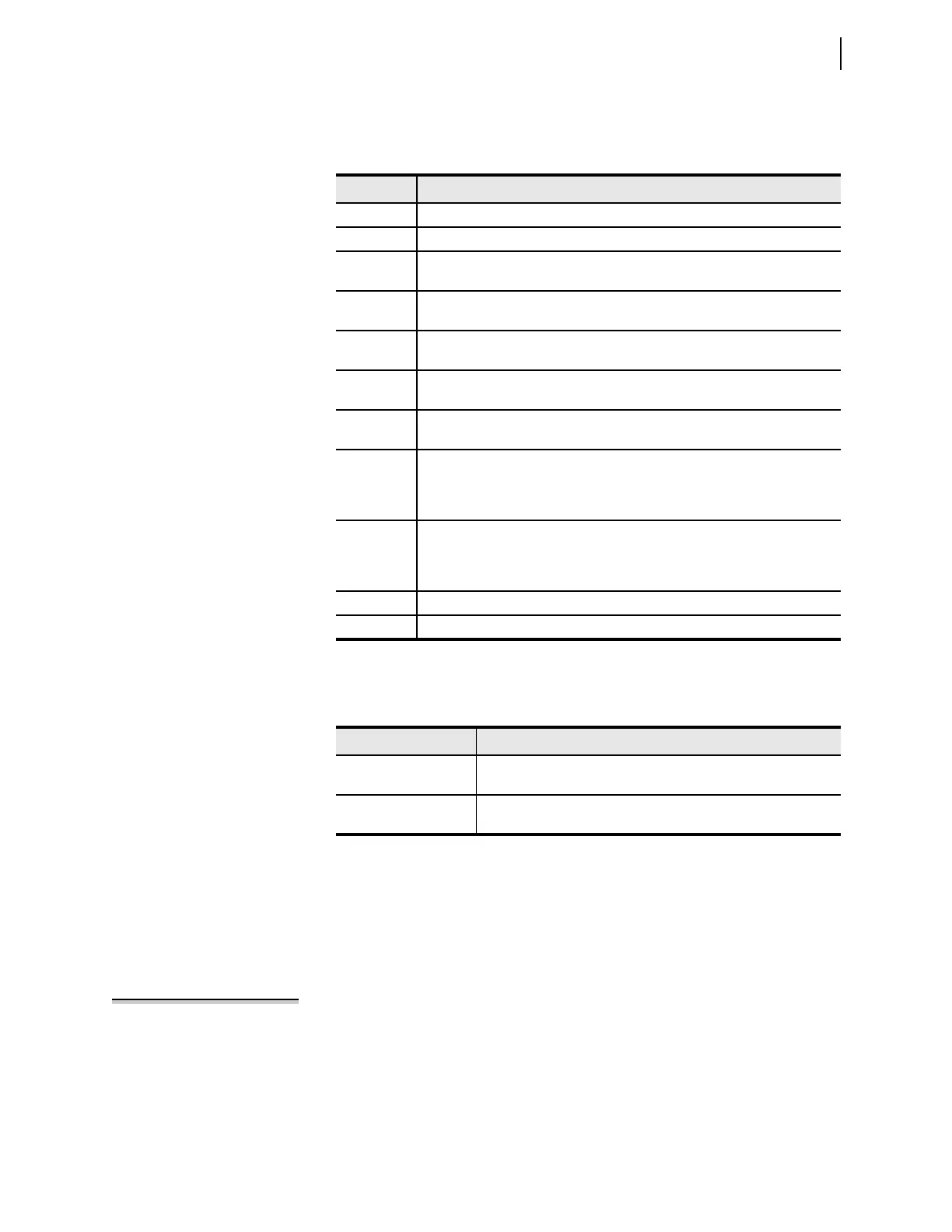

Table 18.10 Remote Synchrophasor Data Bits for Real-Time Control

Name Description

RTCAD01–RTCAD16 First sixteen digitals received in synchrophasor message on

Channel A. Only valid when RTCROKA is asserted.

RTCBD01–RTCBD16 First sixteen digitals received in synchrophasor message on

Channel B. Only valid when RTCROKB is asserted.

NOTE: Sampled Values-subscribing

relays experience a communication

delay in their analog data. Time-

stamping of synchrophasor data is

adjusted by the Port 5 channel delay

setting CH_DLY.

Loading...

Loading...