Interrupts and events UM0306

106/519

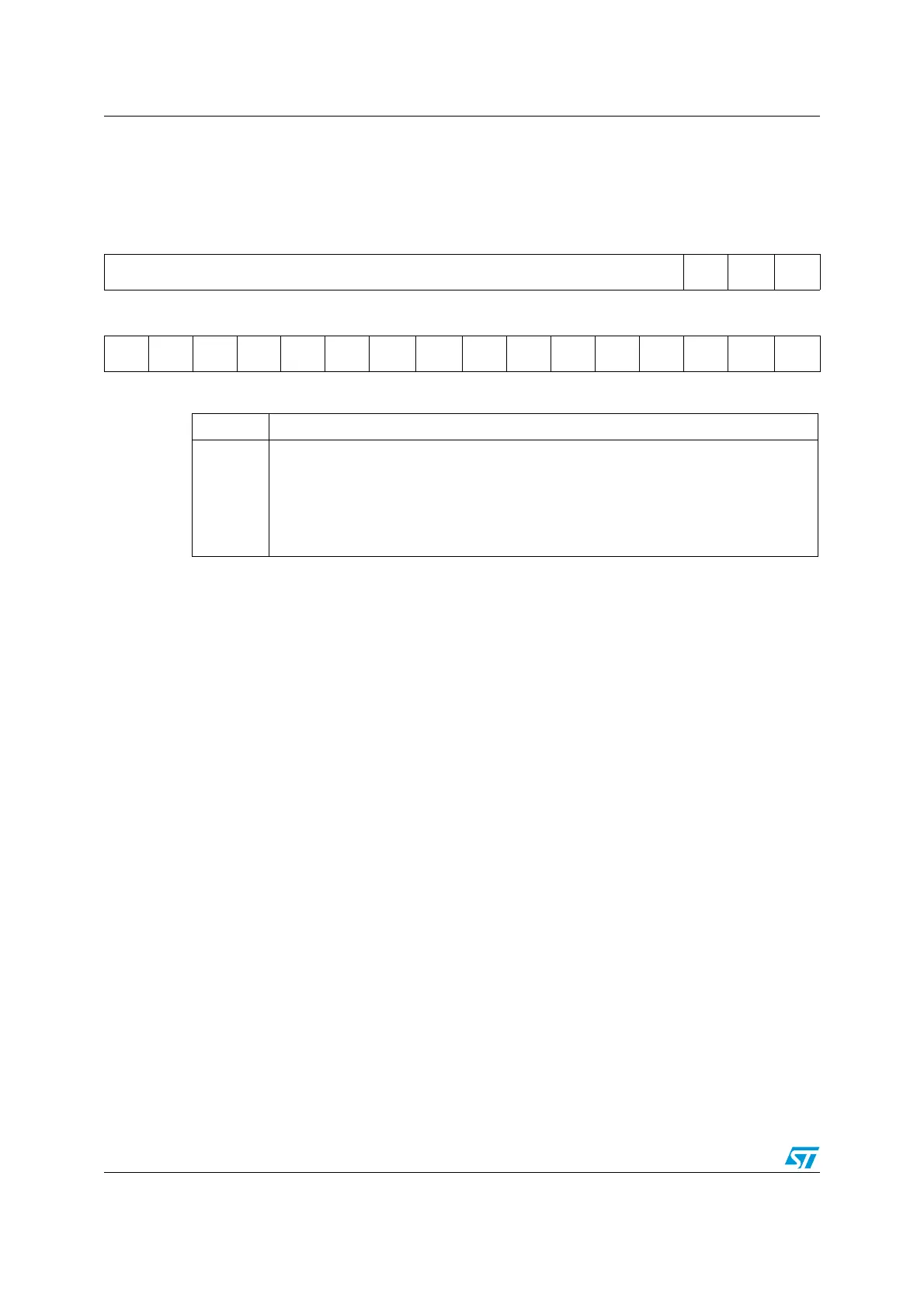

Software interrupt event register (EXTI_SWIER)

Address Offset: 10h

Reset value: 0000 0000h

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved

SWIER

18

SWIER

17

SWIER

16

rw rw rw

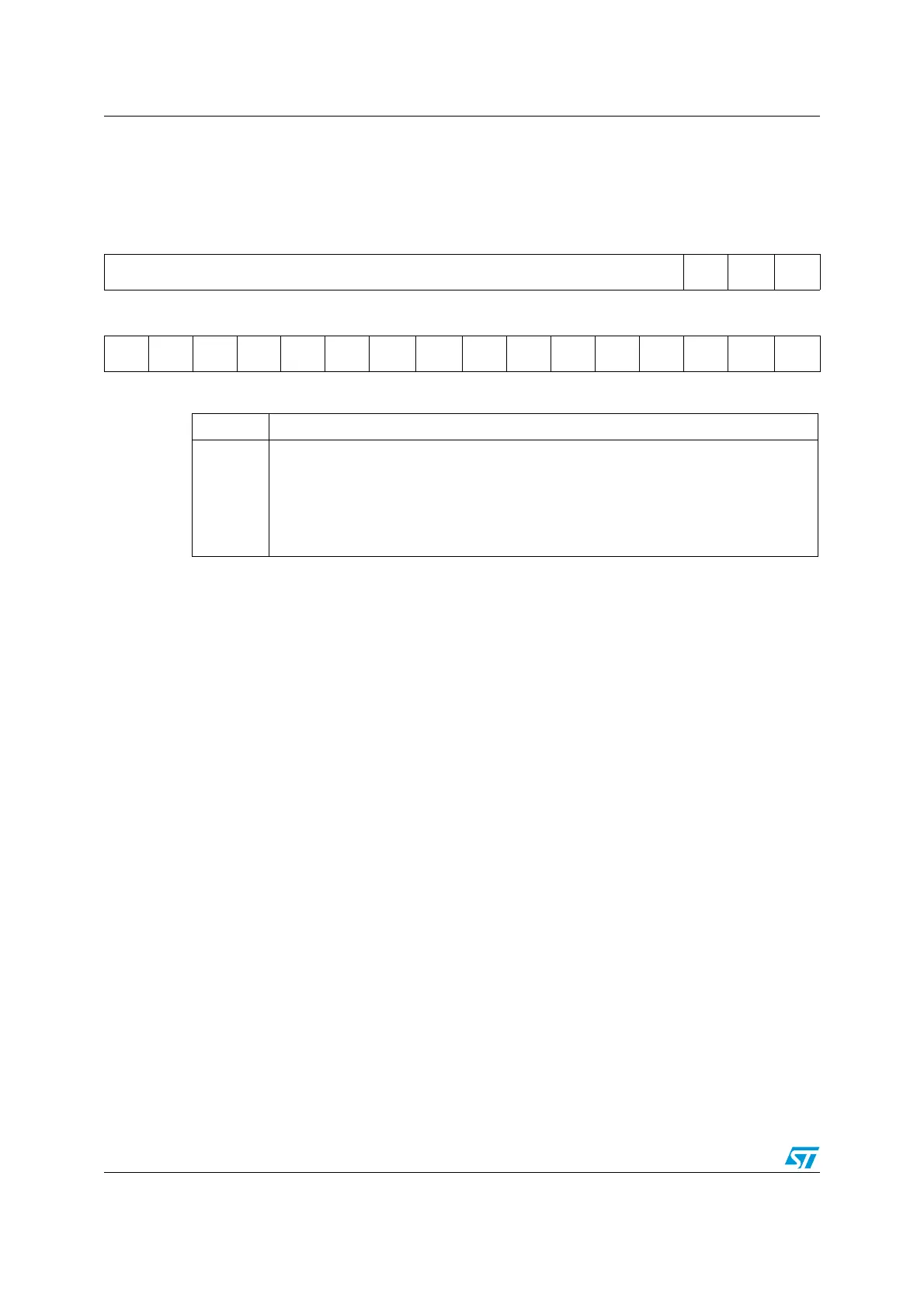

1514131211109 87654321 0

SWIER

15

SWIER

14

SWIER

13

SWIER

12

SWIER

11

SWIER

10

SWIER

9

SWIER

8

SWIER

7

SWIER

6

SWIER

5

SWIER

4

SWIER

3

SWIER

2

SWIER

1

SWIER

0

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:19 Reserved, must be kept at reset value (0).

Bits 18:0

SWIERx: Software Interrupt on line x

Writing a 1 to this bit when it is at 0 sets the corresponding pending bit in EXTI_PR. If

the interrupt is enabled on this line on the EXTI_IMR and EXTI_EMR, an interrupt

request is generated.

This bit is cleared by clearing the corresponding bit of EXTI_PR (by writing a 1 into the

bit).

Loading...

Loading...