UM0306 Analog/digital converter (ADC)

485/519

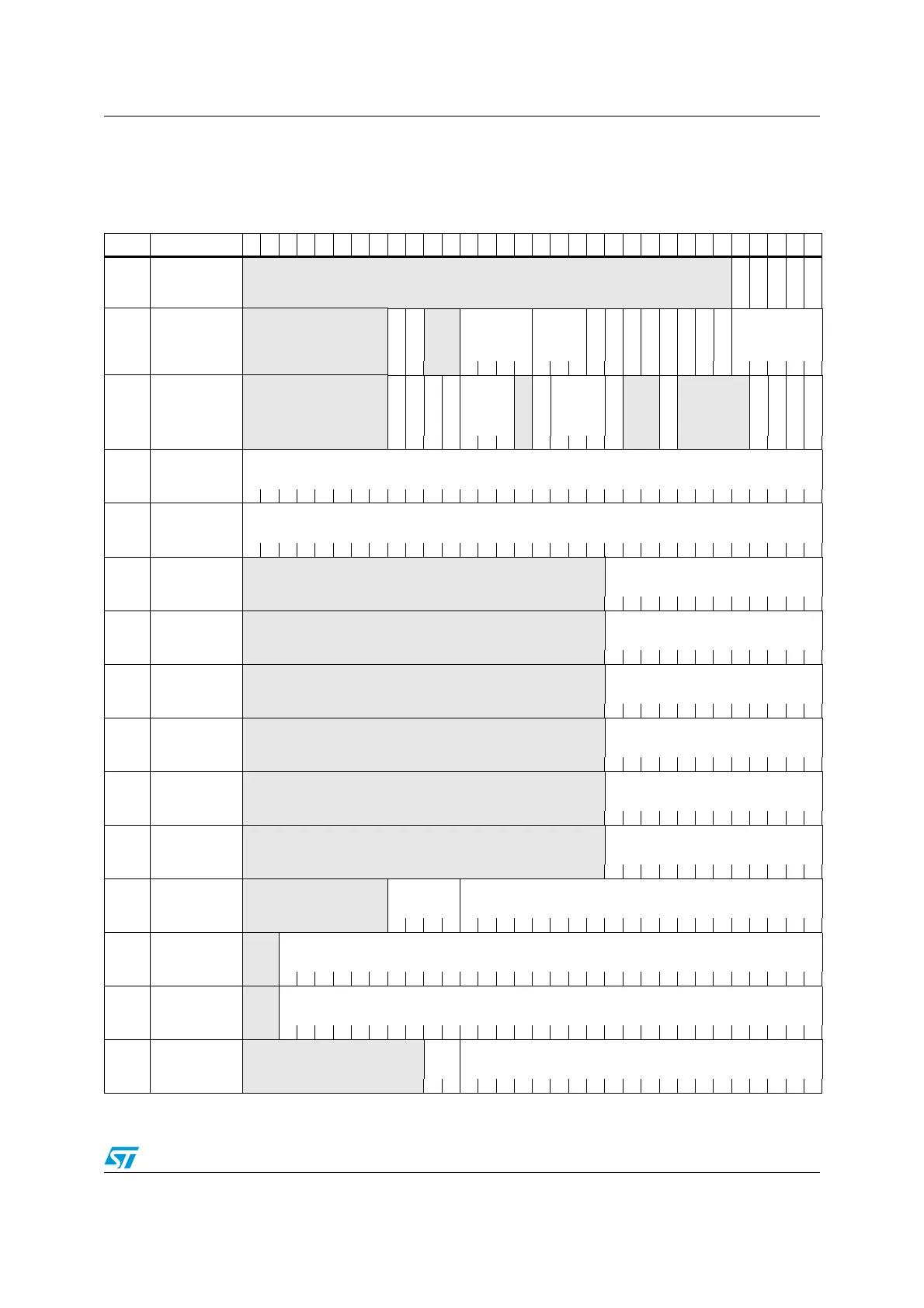

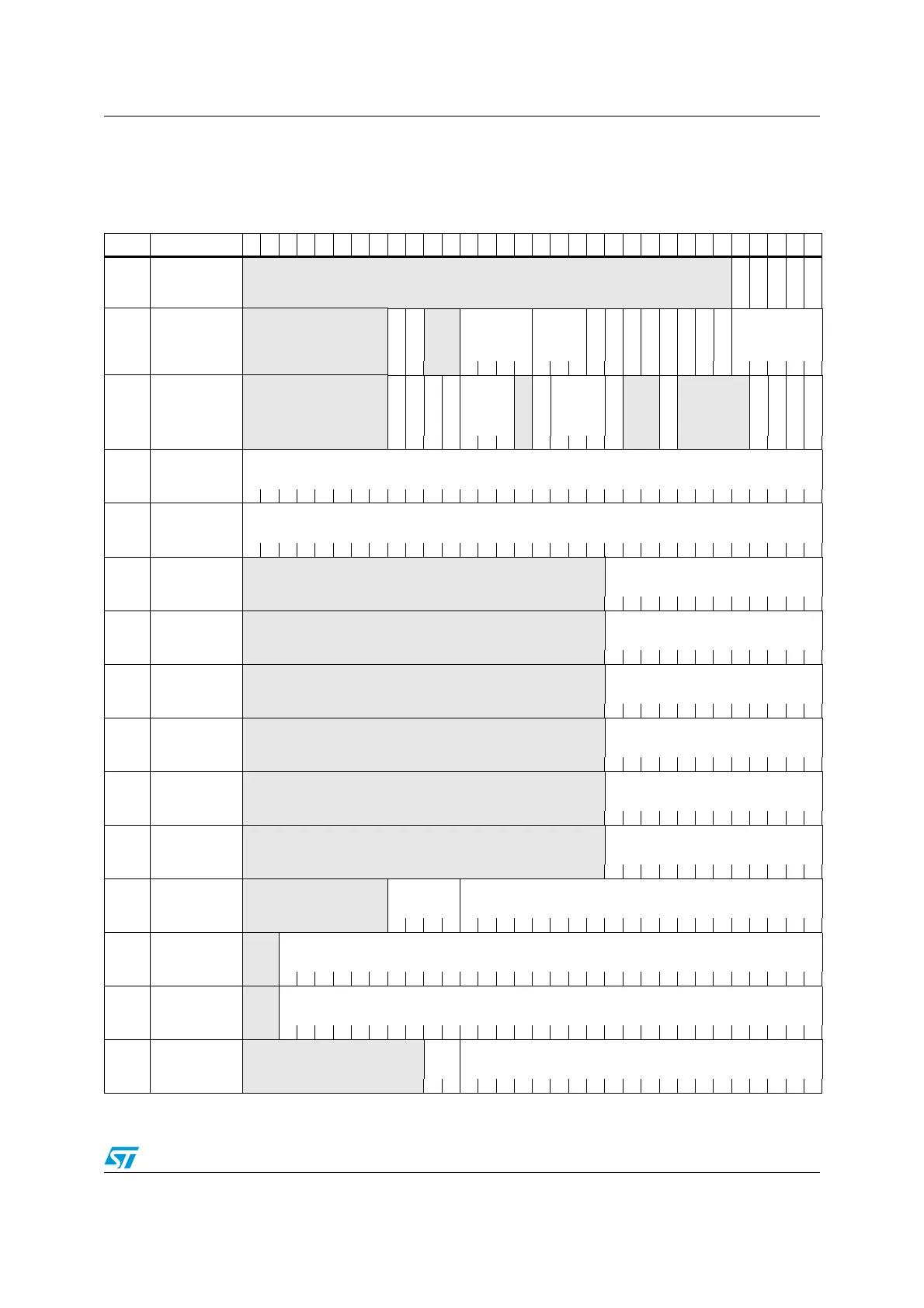

19.14 ADC register map

The following table summarizes the ADC registers.

Table 70. ADC - register map and reset values

Offset Register

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

00h

ADC_SR

Reserved

STRT

JSTRT

JEOC

EOC

AWD

Reset Value 00000

04h

ADC_CR1

Reserved

AWDEN

JAWDEN

Reserved

DUALMOD

[3:0]

DISC

NUM [2:0]

JDISCEN

DISCEN

JAUTO

AWD SGL

SCAN

JEOC IE

AWDIE

EOCIE

AWDCH[4:0]

Reset Value 00 00000000000000000000

08h

ADC_CR2

Reserved

TSVREFE

SWSTART

JSWSTART

EXTTRIG

EXTSEL

[2:0]

Reserved

JEXTTRIG

JEXTSEL

[2:0]

ALIGN

Reserved

DMA

Reserved

RSTCAL

CAL

CONT

ADON

Reset Value 0000000 00000 0 0000

0Ch

ADC_SMPR1 Sample time bits SMPx_x

Reset Value 00000000000000000000000000000000

10h

ADC_SMPR2 Sample time bits SMPx_x

Reset Value 00000000000000000000000000000000

14h

ADC_JOFR1

Reserved

JOFFSET1[11:0]

Reset Value 000000000000

18h

ADC_JOFR2

Reserved

JOFFSET2[11:0]

Reset Value 000000000000

1Ch

ADC_JOFR3

Reserved

JOFFSET3[11:0]

Reset Value 000000000000

20h

ADC_JOFR4

Reserved

JOFFSET4[11:0]

Reset Value 000000000000

24h

ADC_HTR

Reserved

HT[11:0]

Reset Value 000000000000

28h

ADC_LTR

Reserved

LT[11:0]

Reset Value 000000000000

2Ch

ADC_SQR1

Reserved

L[3:0] Regular channel sequence SQx_x bits

Reset Value 000000000000000000000000

30h

ADC_SQR2

Reserved

Regular channel sequence SQx_x bits

Reset Value 000000000000000000000000000000

34h

ADC_SQR3

Reserved

Regular channel sequence SQx_x bits

Reset Value 000000000000000000000000000000

38h

ADC_JSQR

Reserved

JL[1:0] Injected channel sequence JSQx_x bits

Reset Value 0000000000000000000000

Loading...

Loading...