General purpose and alternate function I/O (GPIO and AFIO) UM0306

92/519

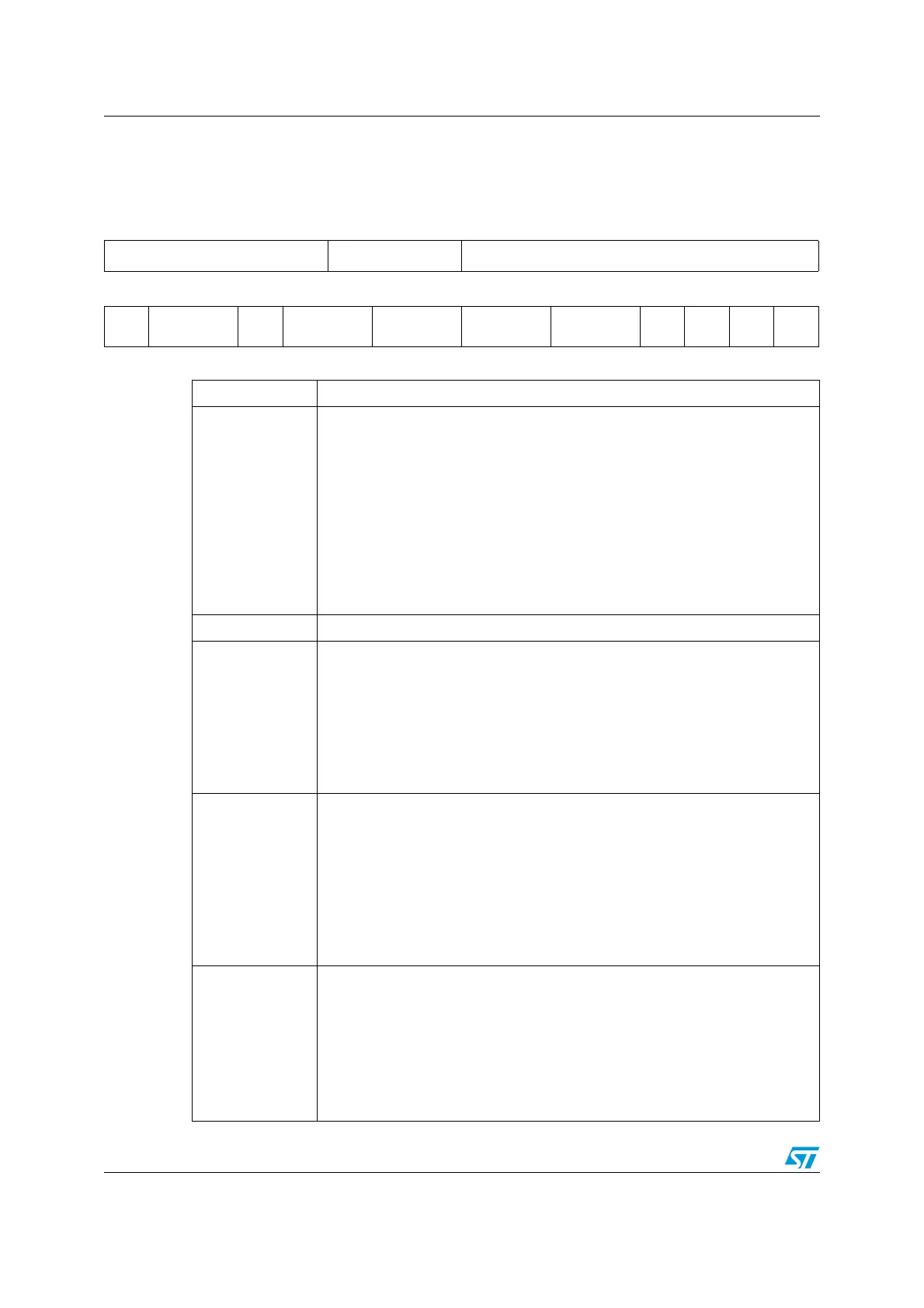

5.4.1 AF remap and debug I/O configuration register (AFIO_MAPR)

Address Offset: 04h

Reset value: 0x0000 0000h

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved

SWJ_

CFG[2:0]

Reserved

rw rw rw

1514131211109876543210

PD01_

REMAP

CAN_REMAP

[1:0]

TIM4_

REMAP

TIM3_REMAP

[1:0]

TIM2_REMAP

[1:0]

TIM1_REMAP

[1:0]

USART3_

REMAP[1:0]

USART

2_

REMAP

USART

1_

REMAP

I2C1_

REMAP

SPI1_

REMAP

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

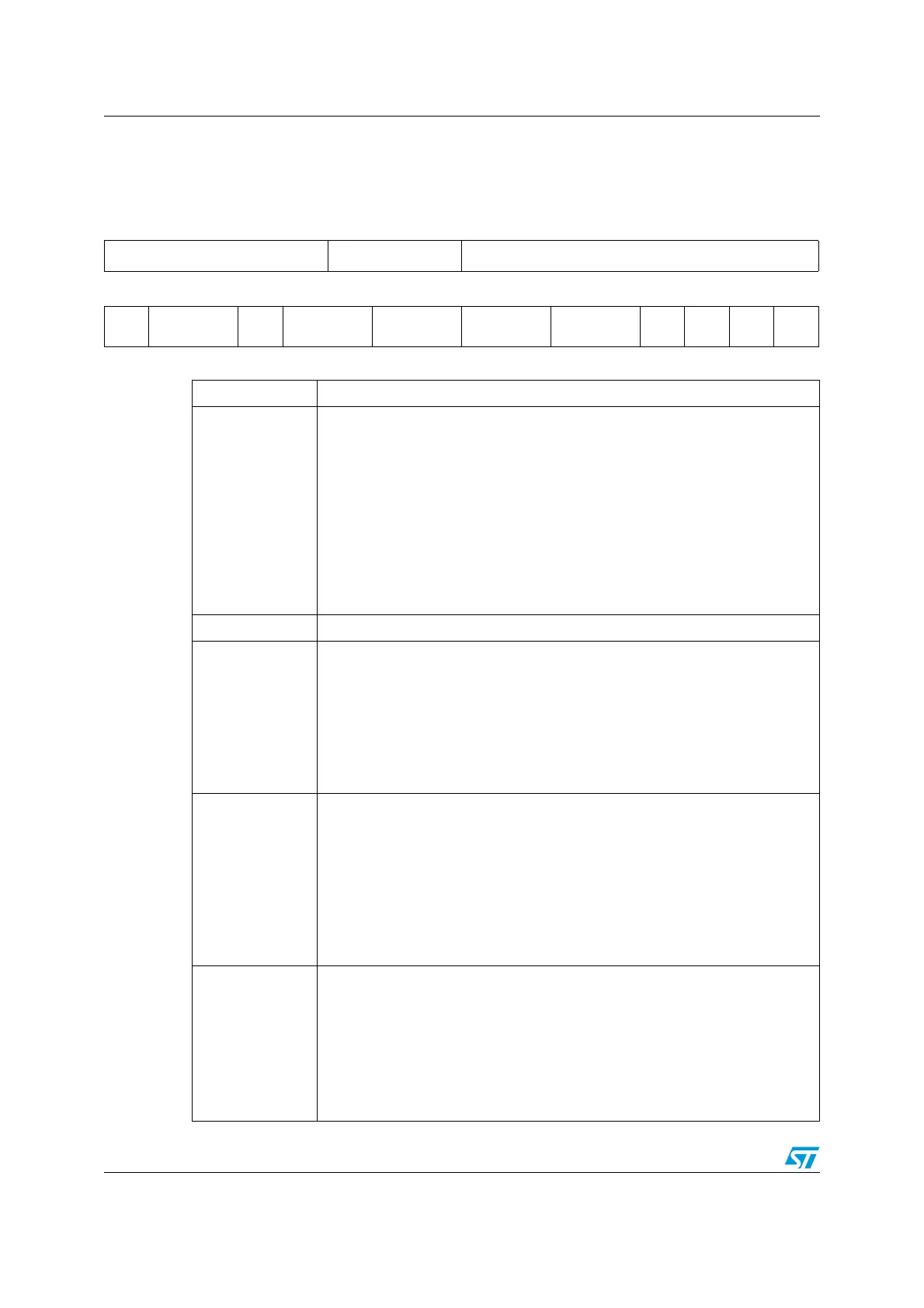

Bits 31:26 Reserved

Bits 25:24

SWJ_CFG[2:0] Serial Wire JTAG configuration

These bits are set and cleared by software. They are used to configure the

SWJ and trace alternate function I/Os. The SWJ (Serial Wire JTAG) supports

JTAG or SWD access to the Cortex debug port. The default state after reset is

SWJ ON without trace. This allows JTAG or SW mode to be enabled by

sending a specific sequence on the JTMS / JTCK pin.

000: Full SWJ (JTAG-DP + SW-DP): Reset State

001: Full SWJ (JTAG-DP + SW-DP) but without JNTRST

010: JTAG-DP Disabled and SW-DP Enabled

100: JTAG-DP Disabled and SW-DP Disabled

Other combinations: Forbidden

Bits 23:15 Reserved

Bit 15

PD01_REMAP: Port D0/Port D1 mapping on OSC_IN/OSC_OUT

This bit is set and cleared by software. It controls the mapping of PD0 and

PD1 GPIO functionality. When the main oscillator is not used (application

running on internal 8 MHz RC) PD0 and PD1 can be mapped on OSC_IN and

OSC_OUT. This is available only on 36, 48 and 64 pin packages (PD0 and

PD1 are available on TQFP100 package, no need for remapping).

0: No remapping of PD0 and PD1

1: PD0 remapped on OSC_IN, PD1 remapped on OSC_OUT,

Bits 14:13

CAN_REMAP[1:0] CAN Alternate function remapping

These bits are set and cleared by software. They control the mapping of

Alternate Functions CANRX and CANTX.

00: CANRX mapped to PA11, CANTX mapped to PA12

01: Not used

10: CANRX mapped to PB8, CANTX mapped to PB9 (not available on 36-pin

package)

11: CANRX mapped to PD0, CANTX mapped to PD1 (available only on 100-

pin package)

Bit 12

TIM4_REMAP TIM4 remapping

This bit is set and cleared by software. It controls the mapping of TIM4

channels 1 to 4 on 100-pin packages only.

0: No remap (TIM4_CH1/PB6, TIM4_CH2/PB7, TIM4_CH3/PB8,

TIM4_CH4/PB9)

1: Full remap (TIM4_CH1/PD12, TIM4_CH2/PD13, TIM4_CH3/PD14,

TIM4_CH4/PD15)

Note: TIM4_ETR on PE0 is not re-mapped.

Loading...

Loading...