DMA controller (DMA) UM0306

112/519

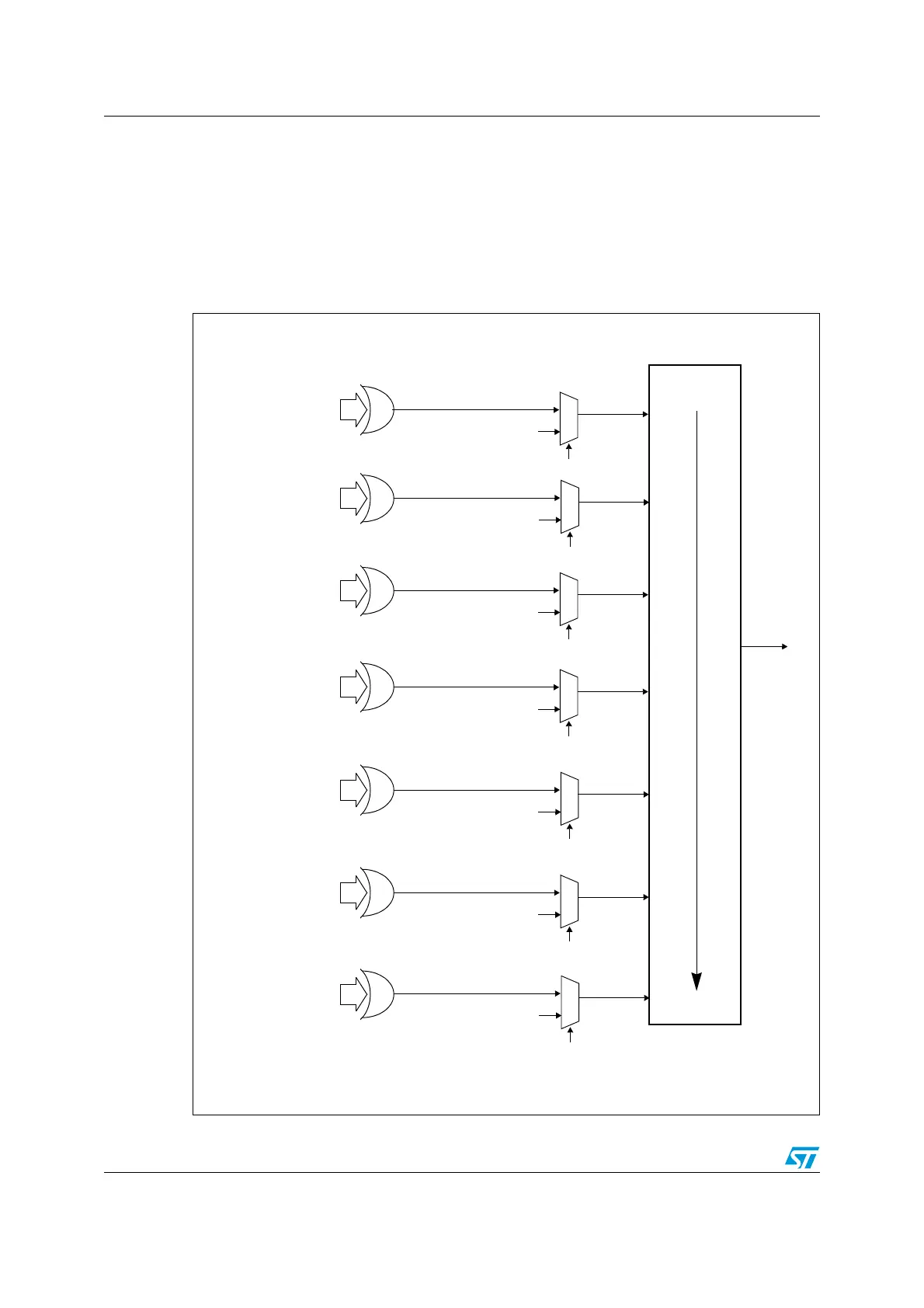

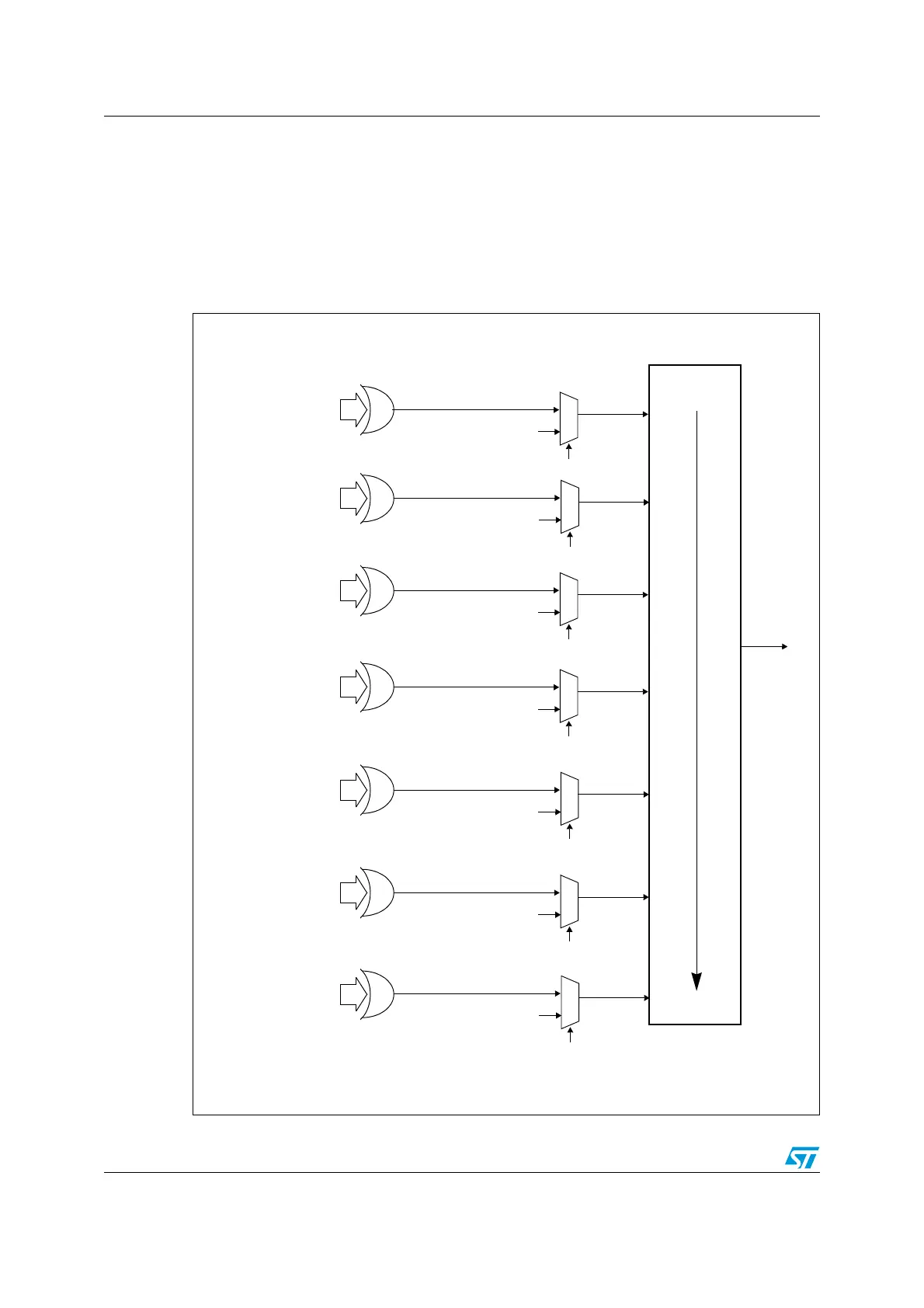

7.3.5 DMA request mapping

The 7 requests from the peripherals (TIMx, ADC, SPIx, I

2

Cx and USARTx) are simply

logically ORed before entering to the DMA, this means that only one request must be

enabled at a time. Refer to Figure 17: DMA request mapping.

The peripheral DMA requests can be independently activated/de-activated by programming

the DMA control bit in the registers of the corresponding peripheral.

Figure 17. DMA request mapping

FIXED HARDWARE PRIORITY

CHANNEL 3

internal

HW REQUEST 3

HIGH PRIORITY

LOW PRIORITY

PERIPHERAL

CHANNEL 2

HW REQUEST 2

CHANNEL 1

SW TRIGGER (MEM2MEM bit)

Channel 1 EN bit

HW REQUEST 1

CHANNEL 4

HW REQUEST 4

DMA

CHANNEL 5

HW REQUEST 5

CHANNEL 6

HW REQUEST 6

CHANNEL 7

HW REQUEST 7

REQUEST

ADC1

USART1_TX

TIM1_CH4

SPI1_TX

USART3_TX

USART1_RX

TIM1_UP

I2C1_TX

TIM3_CH1

I2C1_RX

TIM2_CH2

SPI1_RX

TIM1_CH2

TIM4_CH3

TIM2_CH1

SPI2_TX

I2C2_RX

USART2_RX

TIM3_TRIG

TIM1_CH3

USART2_TX

TIM2_CH4

TIM4_UP

SPI2_RX

I2C2_TX

TIM1_TRIG

TIM4_CH2

TIM3_CH4

TIM3_UP

USART3_RX

TIM3_CH3

TIM1_CH1

TIM2_UP

TIM2_CH3

TIM4_CH1

Channel 2 EN bit

Channel 3 EN bit

Channel 4 EN bit

Channel 5 EN bit

Channel 6 EN bit

Channel 7 EN bit

SW TRIGGER (MEM2MEM bit)

SW TRIGGER (MEM2MEM bit)

SW TRIGGER (MEM2MEM bit)

SW TRIGGER (MEM2MEM bit)

SW TRIGGER (MEM2MEM bit)

SW TRIGGER (MEM2MEM bit)

REQUEST SIGNALS

TIM1_COM

Loading...

Loading...