UM0306 Advanced control timer (TIM1)

179/519

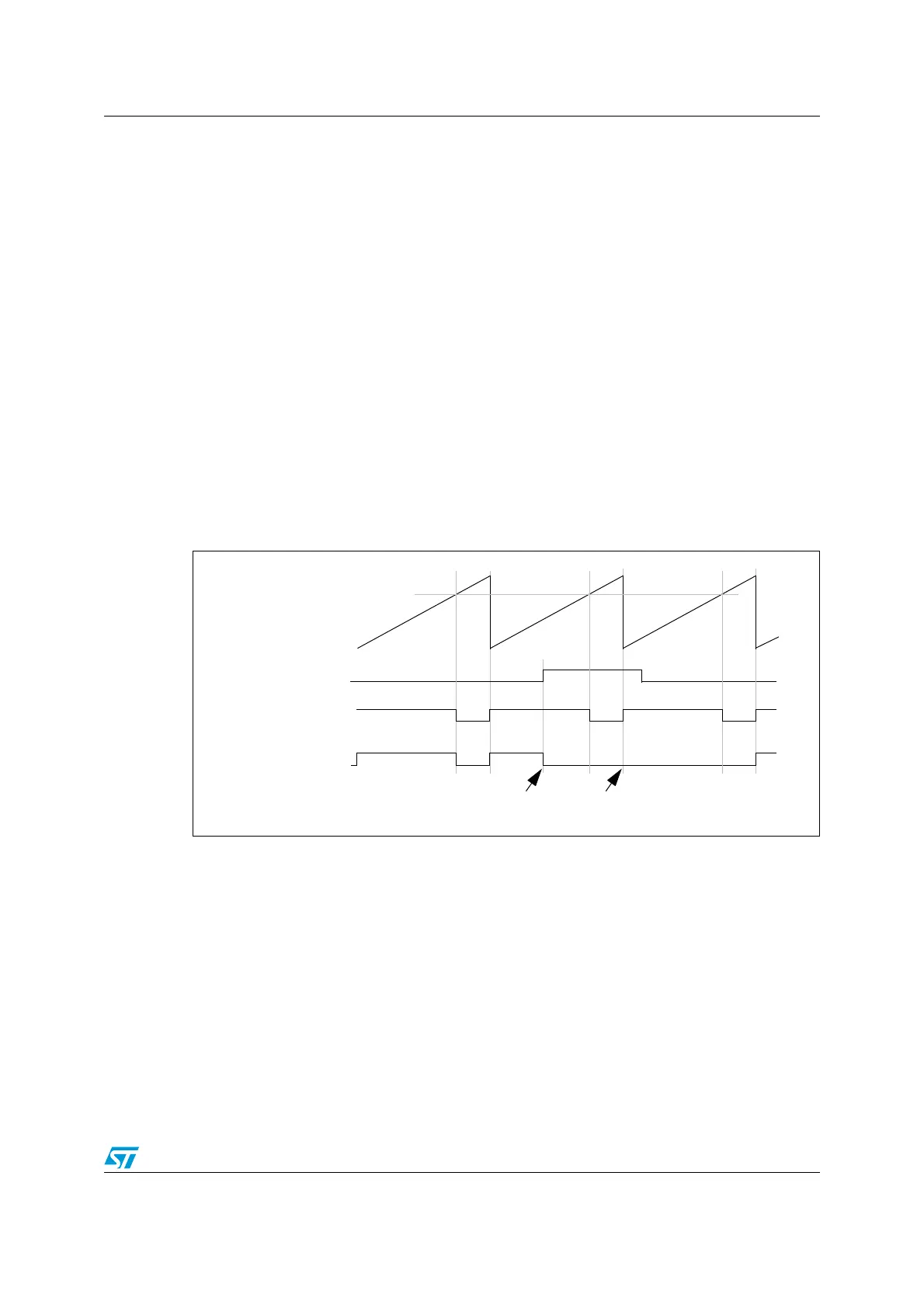

12.4.13 Clearing the OCxREF signal on an external event

The OCxREF signal for a given channel can be driven Low by applying a High level to the

ETRF input (OCxCE enable bit of the corresponding TIM1_CCMRx register set to ‘1’). The

OCxREF signal remains Low until the next update event, UEV, occurs.

This function can only be used in output compare and PWM modes, and does not work in

forced mode.

For example, the OCxREF signal) can be connected to the output of a comparator to be

used for current handling. In this case, the ETR must be configured as follow:

1. The External Trigger Prescaler should be kept off: bits ETPS[1:0] of the TIM1_SMCR

register set to ‘00’.

2. The external clock mode 2 must be disabled: bit ECE of the TIM1_SMCR register set to

‘0’.

3. The External Trigger Polarity (ETP) and the External Trigger Filter (ETF) can be

configured according to the user needs.

Figure 62 shows the behavior of the OCxREF signal when the ETRF Input becomes High,

for both values of the enable bit OCxCE. In this example, the timer TIM1 is programmed in

PWM mode.

Figure 62. Clearing TIM1 OCxREF

OCxREF

counter (CNT)

OCxREF

ETRF

(OCxCE=’0’)

(OCxCE=’1’)

OCREF_CLR

becomes high

OCREF_CLR

still high

(CCRx)

Loading...

Loading...